Part Number: TRF7962A

Other Parts Discussed in Thread: RF37S114, TRF7970A

Hello.

I use the TRF7962A to read the UID of the IC tag [RF37S114].

I occasionally can not read the UID properly.

For example, if reading fails, it will be as follows.

Successful example: 4E 58 A1 66 E 7 C 0 0 7 E 0

Failure example: 4E 58 A1 66 E7 C0 07 52

E0 changes to 52.

If it fails, it always changes to the same number.

When changing to another IC tag, it will change to another number.

Example: E0 -> C1

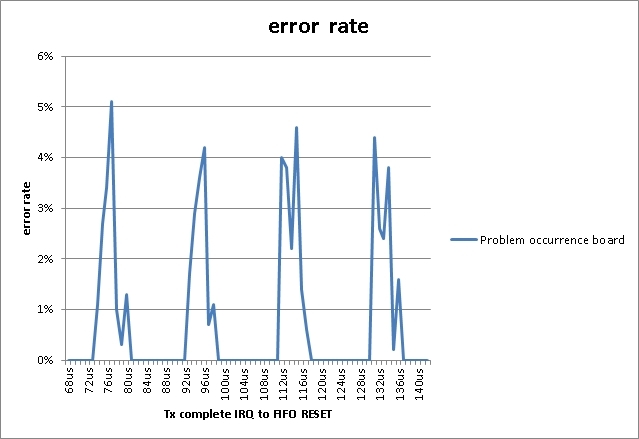

The probability of failing is about 4%.

I know that communication distance affects reading. However, even if communicating at a distance of 0 mm, the result will not change. (In my environment, IC tags can communicate at a distance of 9 mm.)

I use this function to communicate.

Serial Interface Mode With Slave Select (SS)

I saw errata and I got the SPI data on the negative edge. I analyzed the SPI signal by another method, but I got the failed data.

Please tell me what I should be careful in order to get the data correctly.