Other Parts Discussed in Thread: Z-STACK

Tool/software:

Good morning,

in the last few months I worked with zc_thermostat_sink (sdk 4.40) customized version to receive temperature data from a green power sensor.

But the device is designed to perform other tasks in addition to receiving RF data.

The most time consuming is the acquisition from 3 ADC channels @4kHz.

The design is the following:

- An ISR, triggered by a timer related HWI, kicks the ADC conversion for channel 0;

- The EOC ISR copies the value and triggers conversion for channel 1;

- The EOC ISR copies the value and triggers conversion for channel 2;

With the previous version (RF protocol IEEE 802.15.4 and sdk 3.40) all actions were completed with a low jitter.

Now, instead, sometimes happens that timer triggers a new HWI before the acquisition of the 3rd channel is completed.

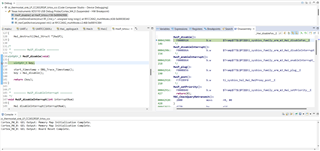

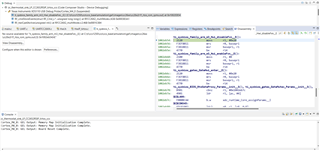

Analyzing the problem by having inserted some trace instructions that write in a circular buffer in ram, I've seen that the OSAL disables all the interrupts, delaying the execution of Timer ISR/EOC ISR for several CPU cycles (even 3700 that @48MHz are about 77µs.).

How can I resolve this situation?

Thanks very much,