Hello Team,

Is there a relationship between PLL1 phase detector frequency setting and output phase noise?

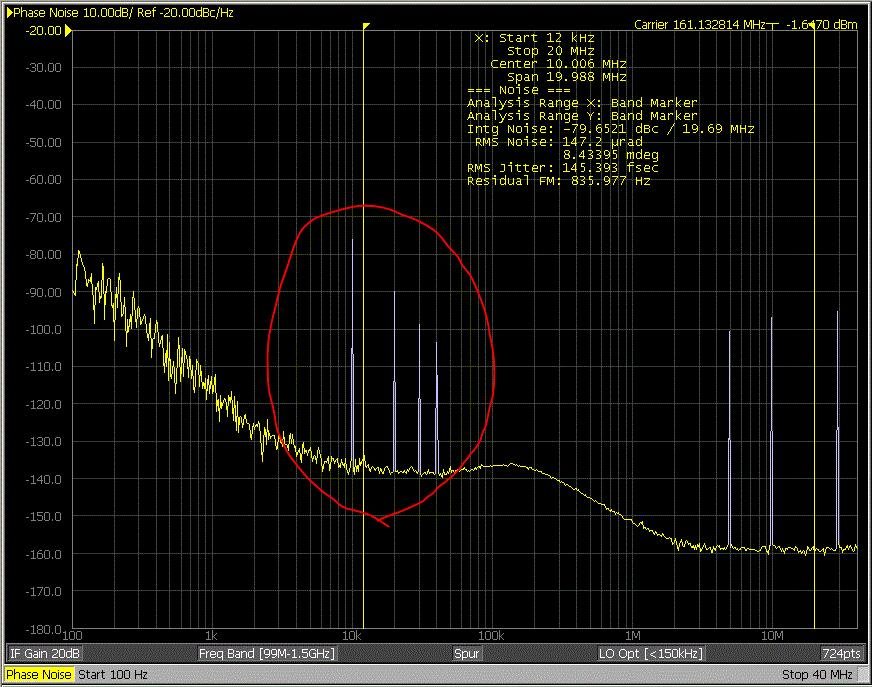

Customer set PLL1 phase detector frequency as 10kHz. When they capture the clock output phase noise, there are high level spur on 10kHz, 20kHz, 30kHz and 40kHz. But when customer increase the PLL1 phase detector frequency like 312.5kHz, there's no spur.

Here is the clock configuration.

CLKin = 30.72MHz

External VCXO = 156.25MHz

OSCin = 156.25MHz

Best regards,

Alice