I find the data sheet specifications Vcm-ac and Vcm-dc confusing.

Assuming 1.80V VDD_Yx_Yy, Vcm-dc is 1.67V (1.80V - 0.13V) and output positive peak would be above VDD_Yx_Yy. This conclusion may be caused by my misunderstanding of the specification. Could you please clarify?

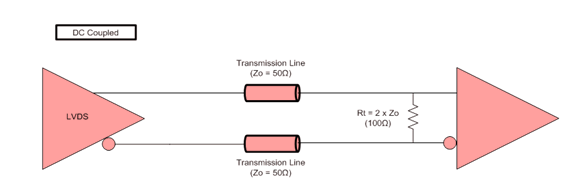

OTOH the Vcm-ac spec is VDD_Yx_Yy-0.76V which would mean 1.04V (VDD_Yx_Yy = 1.80V). Any chance ac and dc specs are swapped in the data sheet? 1.04V Vcm would allow outputs to drive LVDS inputs without AC coupling.

Thank you very much in advance.