Hi,

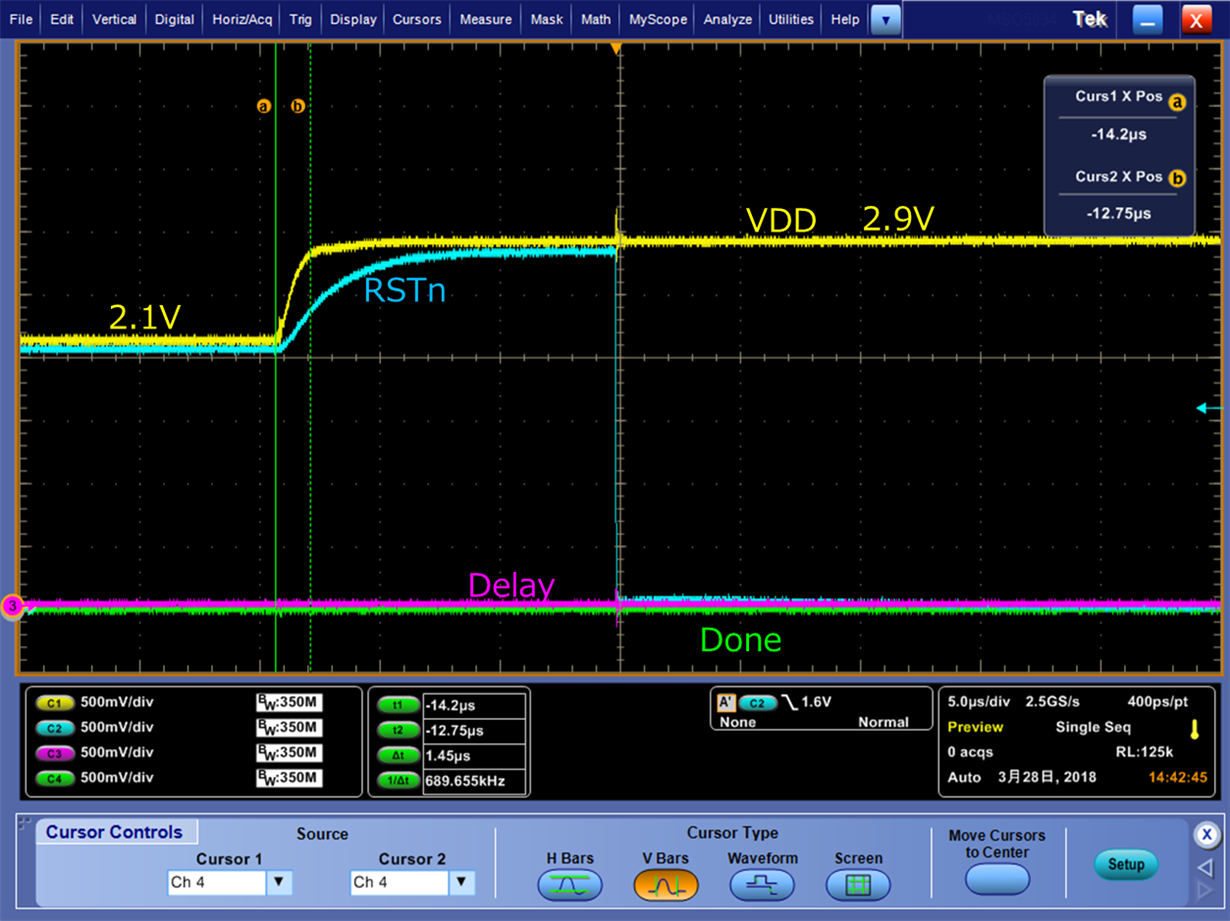

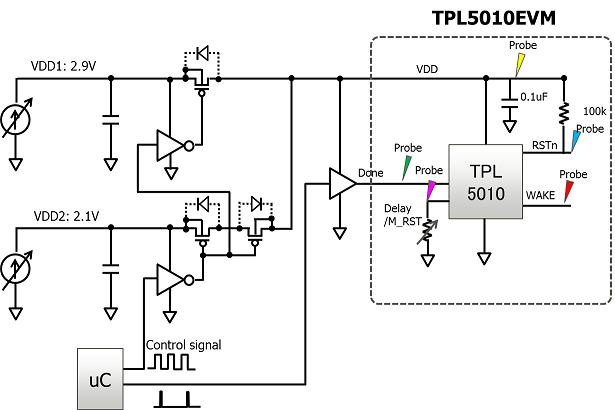

I observed a power on reset phenomenon in TPL5010 when its supply voltage VDD rises up from 2.1V to 2.9V in 1.45us.

The test result is attached. The yellow line is VDD; the light blue line is RSTn; the pink line is Delay signal and the green line is DONE signal.

After a steep increase in VDD, the RSTn signal falls down to 0V and the timer is reset.

Can you tell me what conditions will cause the power on reset phenomenon in TPL5010?

For example, is there a minimum rising slope of VDD that will lead to the power on reset?

(the rising slope of VDD=ΔV/Δt, where the ΔV represents the increased value of VDD, Δt represents the time that it takes for VDD to rise up.)

I think it may be quicker to draw the conclusion by running a simulation.

I am wondering how the circuit works when the VDD rises up. It will be very helpful if you could provide me with a detailed block diagram of TPL5010.

I asked the same question 9 days ago. But it is still not answered.

I would appreciate if you could answer my question quickly.

Sincerely,

Hong