Other Parts Discussed in Thread: TINA-TI, , ADS1298

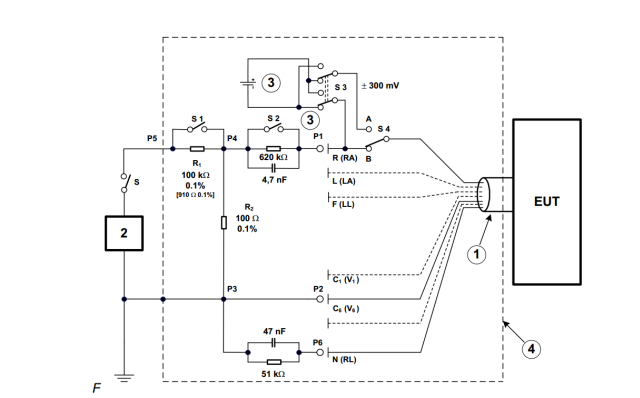

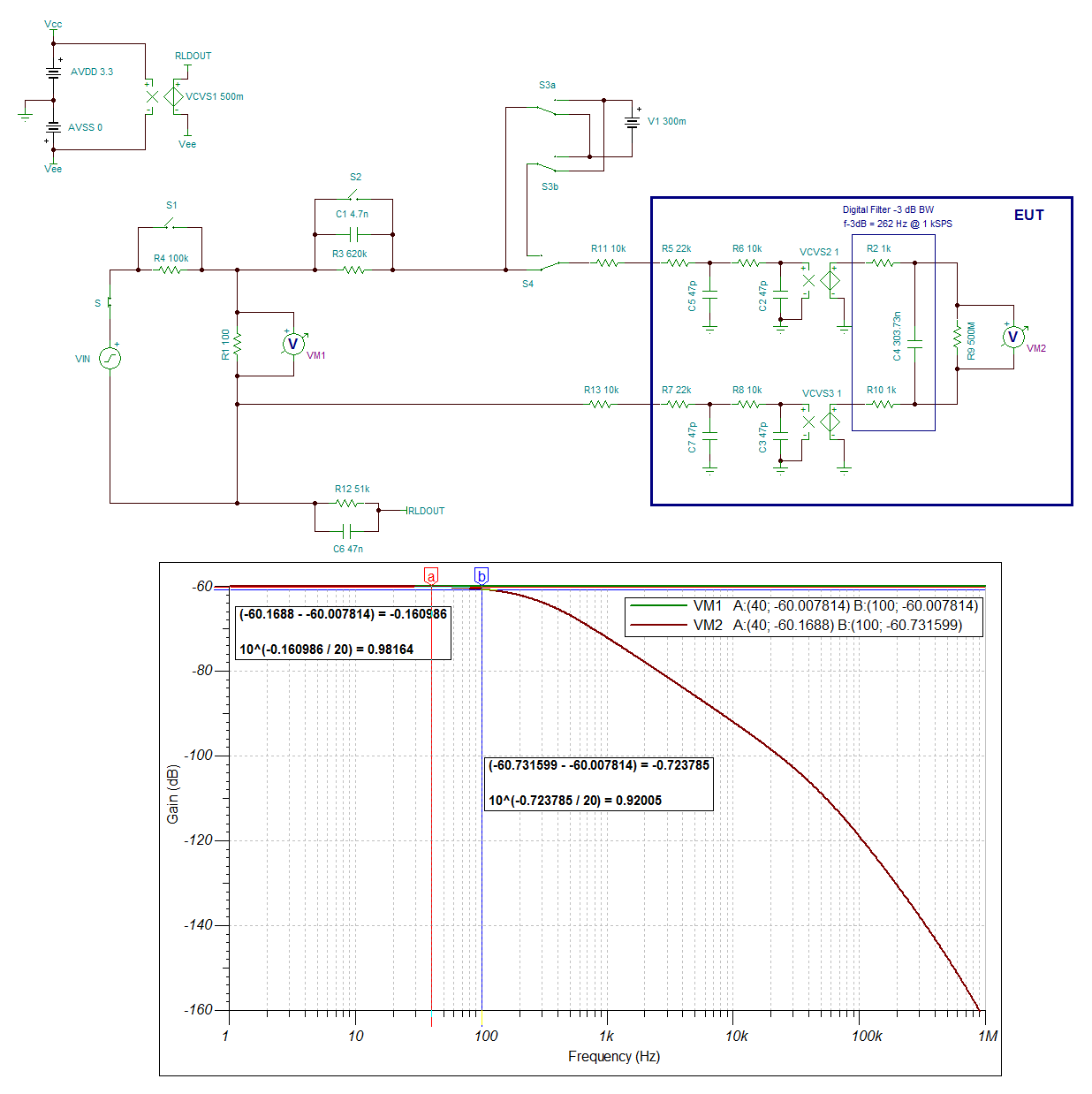

Hello. We have an ECG device with ADS1298R. We need to pass IEC_60601-2-27 and we have some doubts according sub clause 201.12.1.101.3. It is related to the input impedance measurement. The test is to connect a parallel RC network 620k || 4.7nF in series with tested electrode.

The idea is to compare the voltage level with and without series impedance. The difference must be less then 20% to pass the test. The test signal is sinus with frequency 0.67Hz and 40Hz.

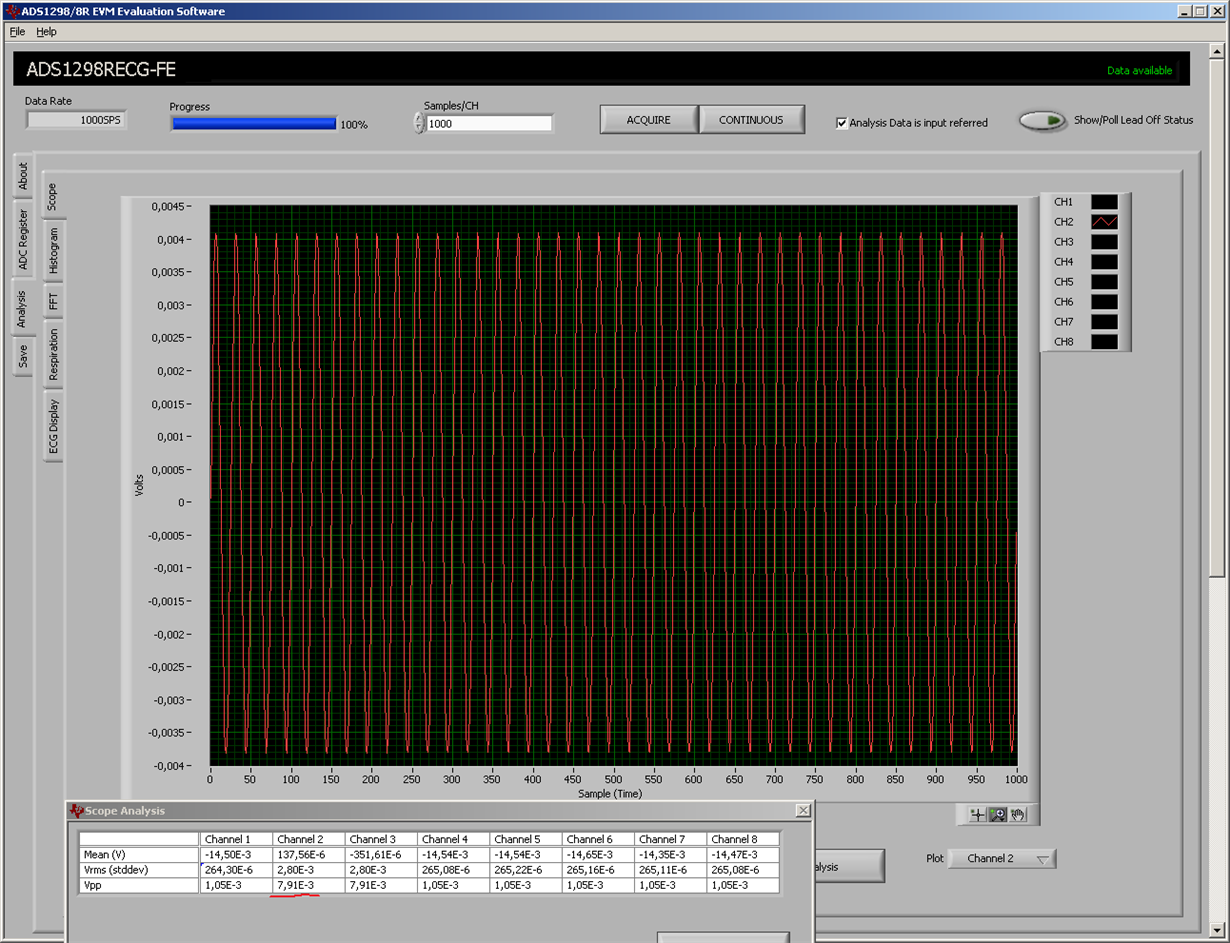

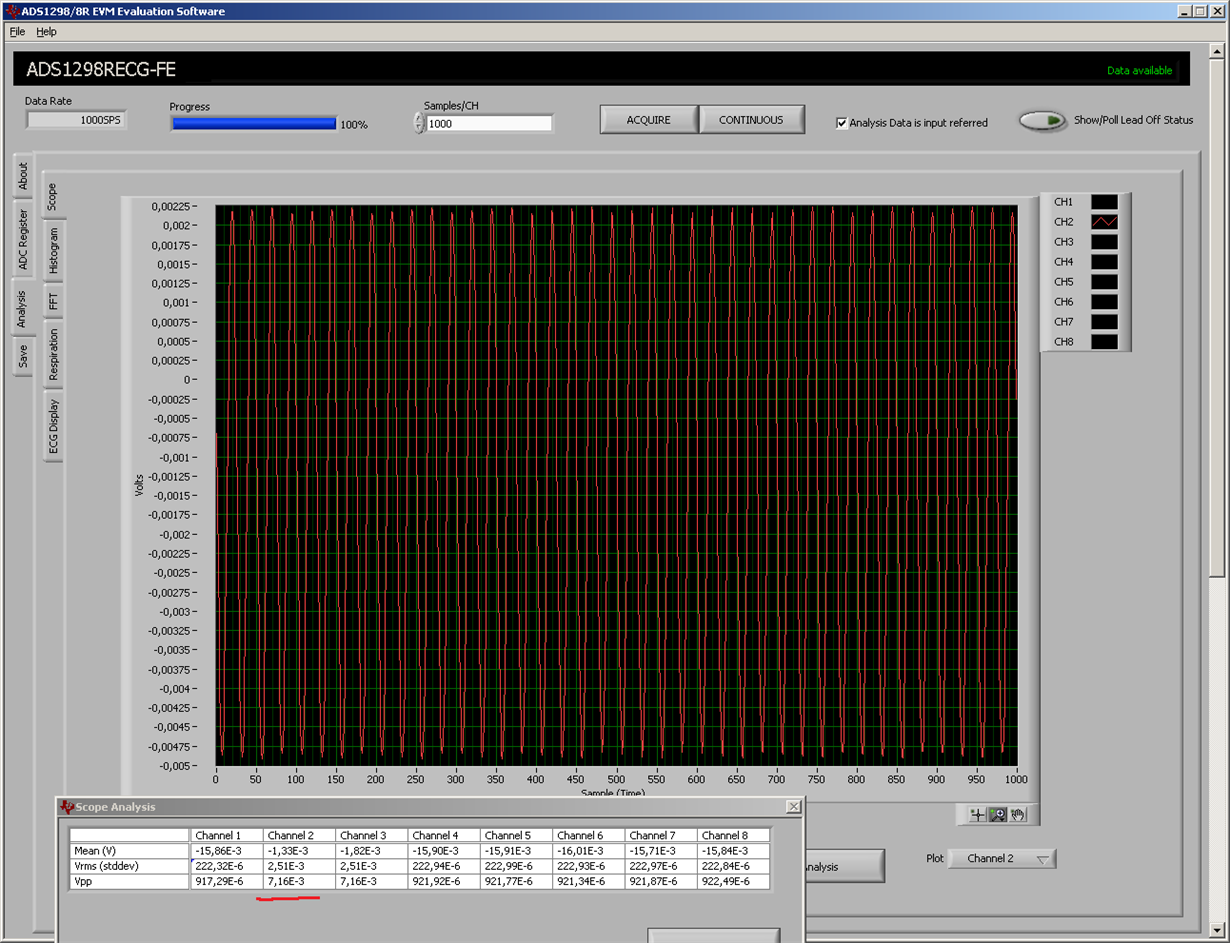

With 0.67Hz there is insignificant voltage drop, we are passing the test clearly. With 40Hz we have a voltage drop of about 12%. So we can pass the test, also.

But what I want to know is - why we have this voltage drop on higher frequencies?

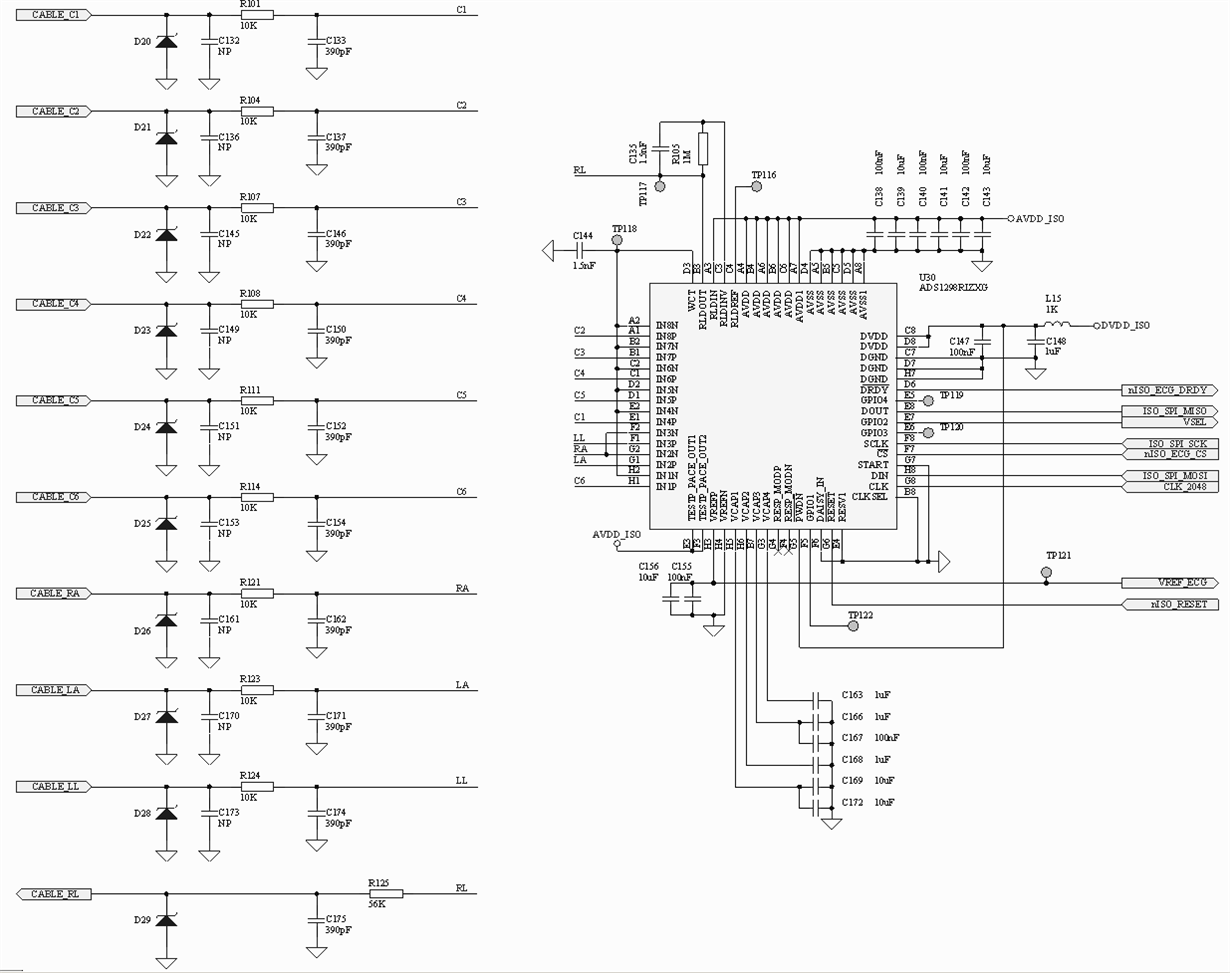

Our input circuit includes simple RC filter 10Kohm || 680pF. We have also a 10Kohm protection in series in the ECG cable. There is a TVS diode in parallel but it's capacitance is really small -few pF.

So normally the input circuit during the test consists a total resistance of 640kOhm and 700pF capacitance. This is a filter with pole 350Hz. For frequency of 40Hz it should have 0.058dB magnitude decrease, or around 1% amplitude decrease.

But during my experiments I'm seeing a drop of about 10-12% on 40Hz. And the voltage drop is clearly frequency dependent. On 1Hz we don't have decreasing, on 10Hz becomes visible, on 40Hz it is 10-12%, on 100Hz it is really significant. Due to my simple calculations this is equal to parallel capacitance of about 3nF, which is not existing in my schematics.

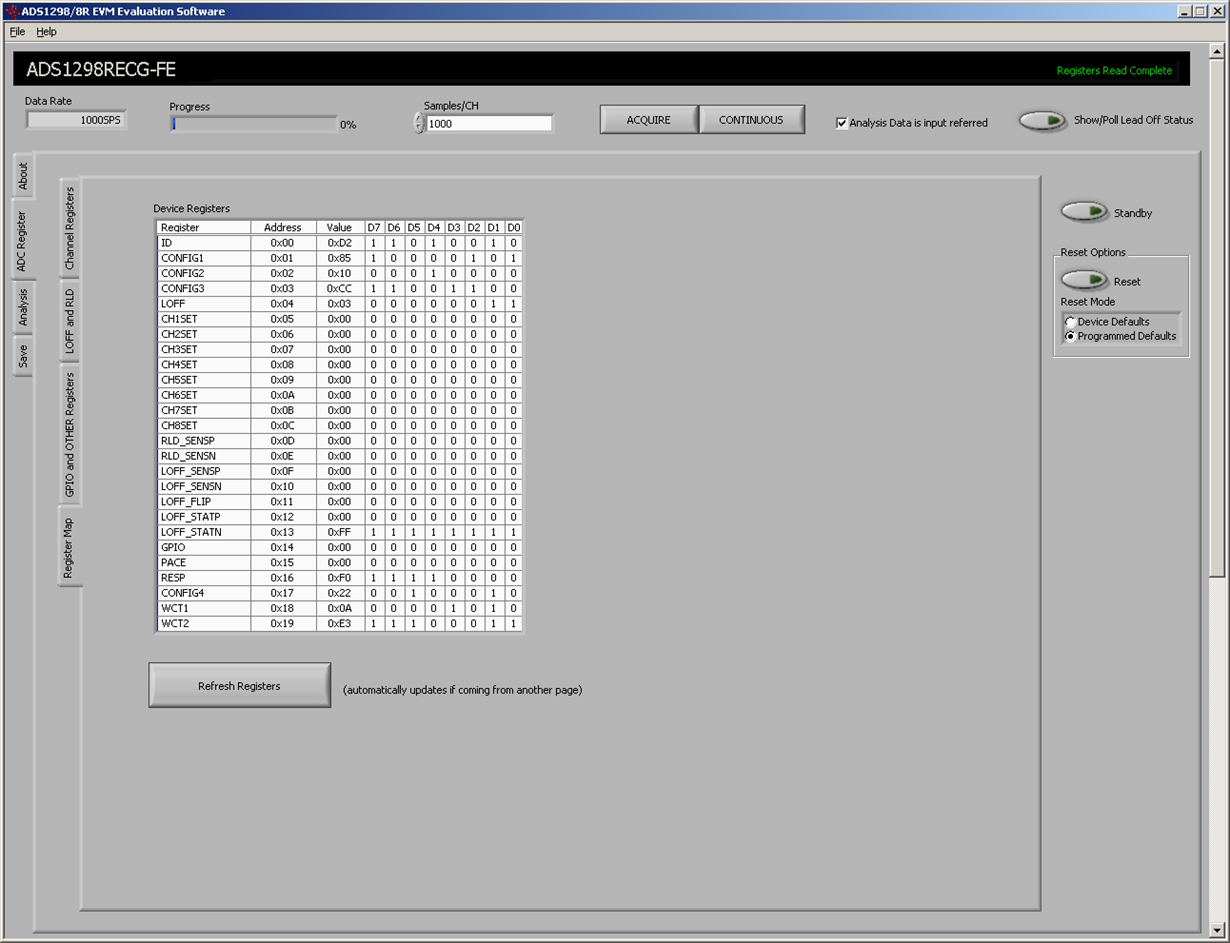

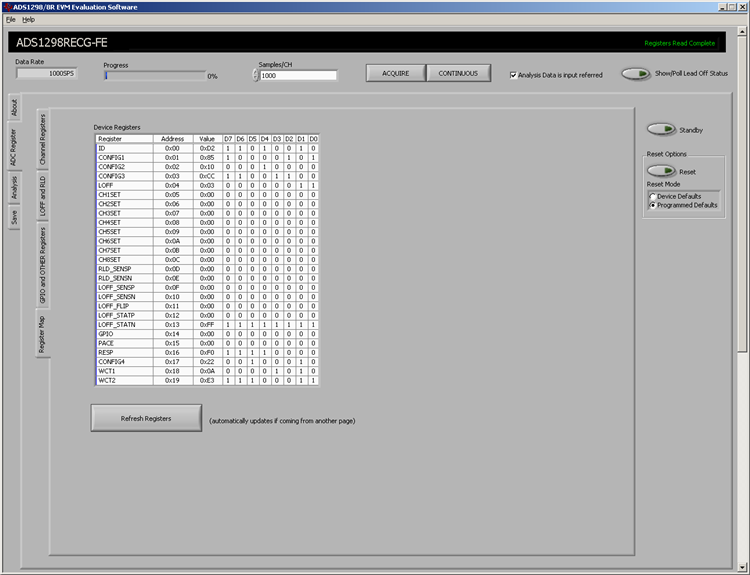

We are using active right leg driving. To exclude RLD influence, I'm setting the RLD_SENSP and RLD_SENSN registers to 0x00. This should eliminate a frequency back loop and the RLD amplifier works like a voltage follower, .we are useing it just for body polarization to the middle of the power supply. But we still have the same issue - 40Hz drops with 10-12%.

We have a 2nd order notch filter on 50Hz in the software. But it acts in both cases - with and without 620k connection. The test is relative, so normally this 50Hz notch should not has an impact in test result. Anyway - I tried with 50Hz filter off. There is more noise in this case, but the 40Hz decrease is clearly visible again.

So my question is - what else can provoke this voltage drop on 40Hz when 620kohm is connected in series?