Tool/software: Code Composer Studio

hello,

in the past we developed a custom board with the TMS320C6678ACYP (with A in the upper right of the device) and a SPI device N25Q128A11BSF40F; the BOOTMODE[12:0] pins was set in the following mode: 0101100000110 (boot from SPI). the CORE CLK was 100 MHz and DDRCLK 66,6667 MHz. we built 4 boards and we didn't had any problems.

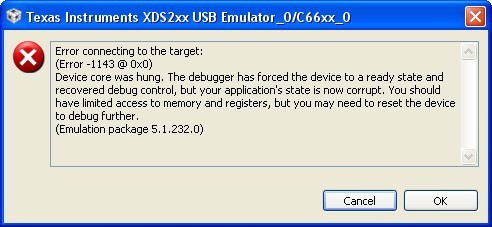

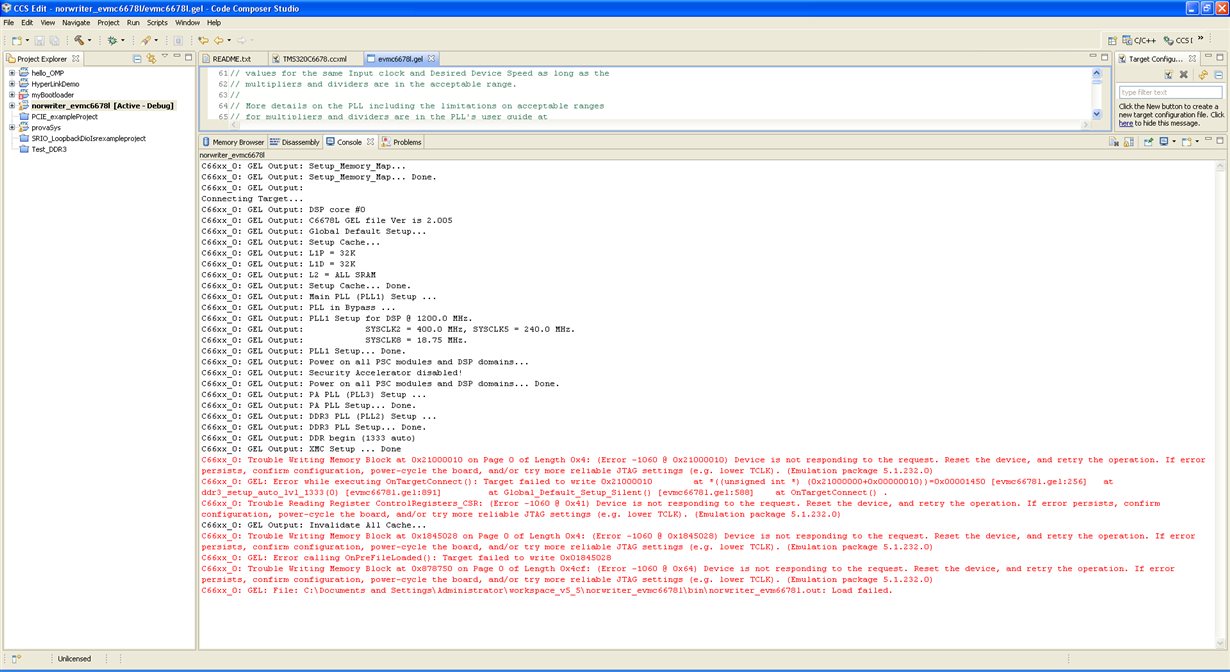

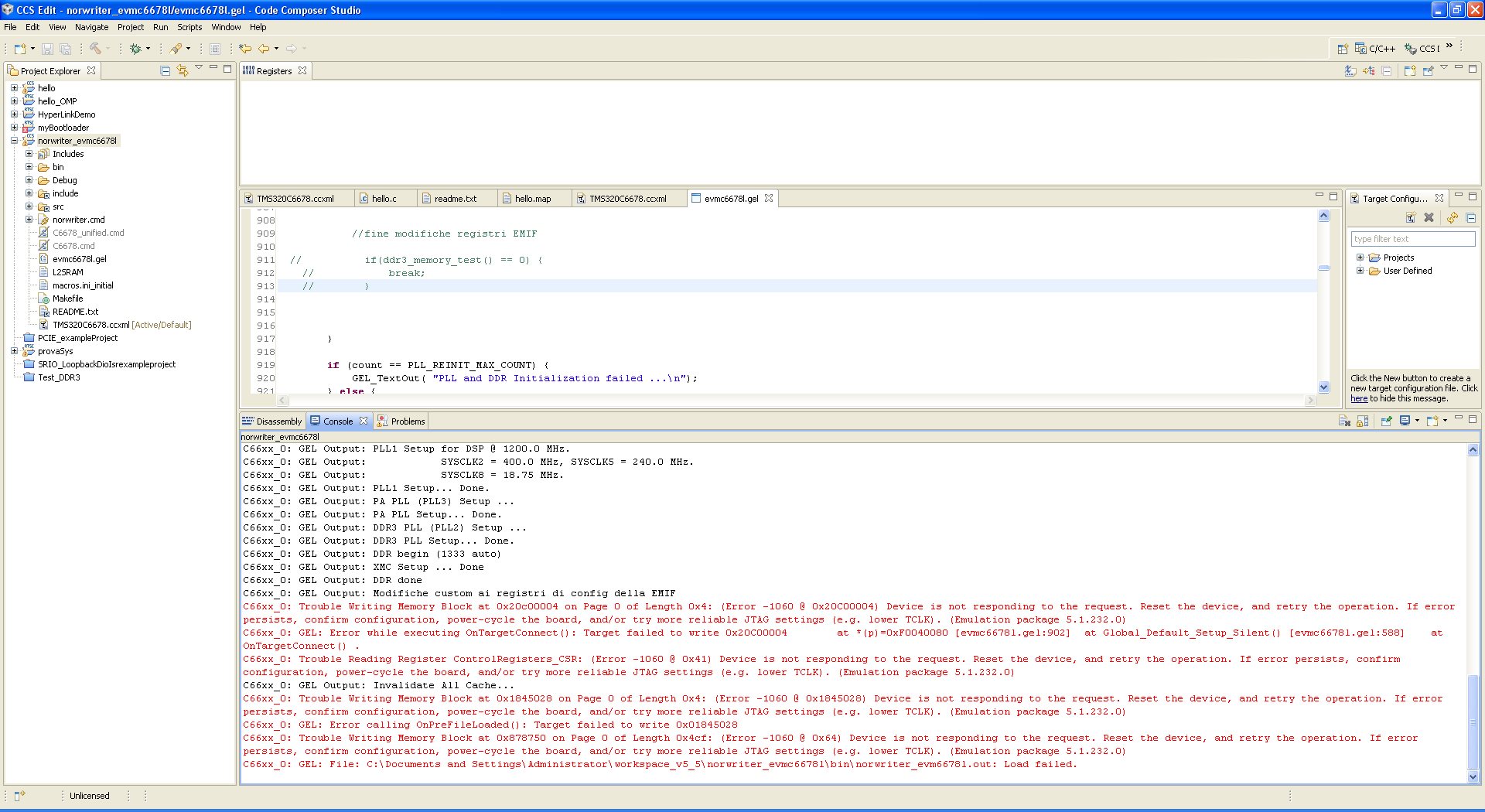

now, we have rebuilt 6 six more boards, identically to the previous one, except for the DSP, changed to the 1,25 GHz version (A1.25GHZ in the upper right of the device). With this configuration, we are not able to connect with the JTAG emulator (USB200 jtag emulator), and the following error is shown:

do you have any suggestion about this?

thanks in advance

Fabrizio Gualtieri