Hi,

I'm working on LCDK6748 with TIRTOS v. 2.0.1.23 , XDC 3.30.3.47 and CCS v6.0.1.00040. Codec is AIC3106 and DSP is OMAPL138. I wrote a simple program to perform Audio Echo chanel sample by sample. I'm generating sine wave with 400Hz and amplitude 390mV. My code alows me to acquire sine wave :

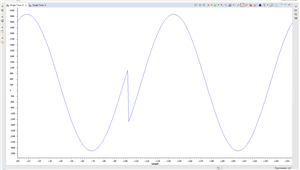

,but returned signal is heavily distorted :

I have no idea what is the issue of this distortion. Is anybody have any clue what am I doing wrong? Below I attach file with my init codes for McAsp, codec and with main().

Thanks,

Best Regards

Mirek

int main(void)

{

/*PinMuxSetup for all peripherals*/

I2CPinMuxSetup(0);

McASPPinMuxSetup();

/*PowerUp modules */

PSCModuleControl(SOC_PSC_1_REGS, HW_PSC_MCASP0, PSC_POWERDOMAIN_ALWAYS_ON,

PSC_MDCTL_NEXT_ENABLE);

BIOS_start();

}

void runningThread(void)

{

/* i2c init */

I2CCodecIfInit(SOC_I2C_0_REGS ,INT_CHANNEL_I2C , I2C_SLAVE_CODEC_AIC31);

/* codec configuration */

codecInit();

/* mcasp configuration */

McASPConfigure();

while(1)

{

/* loop */

}

}

/* McAsp ISR */

void McASP_ISR(void)

{

Sample = McASPRxBufRead(SOC_MCASP_0_CTRL_REGS, MCASP_XSER_RX);

Swi_post(AudioSWI);

}

/* SWI */

void AudioProcessSWI(void)

{

static UInt j =0,k =0;

/* Data from left channel */

if(HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_RSLOT))

{

Buffer[j]=(Int16)Sample;

//Sample = Buffer[j];

j+=1;

j= j%256;

}

else

{

Buffer2[k]=(Int16)Sample;

k+=1;

k= k%256;

Sample = 0 ;

}

while(!(HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XSTAT)&0x20)); /* wait untill empty */

McASPTxBufWrite(SOC_MCASP_0_CTRL_REGS, MCASP_XSER_TX,Sample);//(Int)sinetable[i]);

while((HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XSTAT)&0x20)); /* wait untill full */

}

/* AIC3106 configuration: */

/* Set the sample Rate */

CodecRegWrite(baseAddr, AIC31_P0_REG2, 0x00);

CodecRegWrite(baseAddr, AIC31_P0_REG3, 0x22);

/* use PLL_CLK_IN as MCLK */

CodecRegWrite(baseAddr, AIC31_P0_REG102, 0x00);

/* Use PLL DIV OUT as codec CLK IN */

CodecRegBitClr(baseAddr, AIC31_P0_REG101, 0x01);

/* Select GPIO to output the divided PLL IN */

//CodecRegWrite(baseAddr, AIC31_P0_REG98, 0x20);

CodecRegWrite(baseAddr, AIC31_P0_REG4, 0x40);

/* Configure the PLL divide registers */

CodecRegWrite(baseAddr, AIC31_P0_REG5, 0x6D);

CodecRegWrite(baseAddr, AIC31_P0_REG6, 0x60);

CodecRegWrite(baseAddr, AIC31_P0_REG11, 0x01);

/* Enable the codec to be master for fs and bclk */

CodecRegWrite(baseAddr, AIC31_P0_REG8, 0x00); /* Slave Mode */

//CodecRegWrite(baseAddr, AIC31_P0_REG8, 0xD0); /* Master Mode */

CodecRegWrite(baseAddr, AIC31_P0_REG7, 0x0A);

/* Write the data type and slot width */

CodecRegWrite(baseAddr, AIC31_P0_REG9, 0x06);

/* valid data after dataOff number of clock cycles */

CodecRegWrite(baseAddr, AIC31_P0_REG10, 0x00);

/* ADC Mono */

/* enable the programmable PGA for left and right ADC */

CodecRegWrite(baseAddr, AIC31_P0_REG15, 0x00);

CodecRegWrite(baseAddr, AIC31_P0_REG16, 0x80); /* Right ADC is muted */

/* power off the Line L1L */

CodecRegWrite(baseAddr, AIC31_P0_REG19, 0x04);

/* power on the Line LIR */

CodecRegWrite(baseAddr, AIC31_P0_REG22, 0x00);

/* power up the left and right(off) DACs */

CodecRegWrite(baseAddr, AIC31_P0_REG37, 0xA0);

/* select the DAC L1 R1 Paths */

CodecRegWrite(baseAddr, AIC31_P0_REG41, 0x00); /* Mono settings */

CodecRegWrite(baseAddr, AIC31_P0_REG42, 0x6C); /* Driver power-on time/ ramp-up step time*/

/* DAC L to HPLOUT Is NOT connected */

CodecRegWrite(baseAddr, AIC31_P0_REG47, 0x7F);

CodecRegWrite(baseAddr, AIC31_P0_REG51, 0x7F);/* is off*/

/* DAC R to HPROUT is NOT connected */

CodecRegWrite(baseAddr, AIC31_P0_REG64, 0x7F);

CodecRegWrite(baseAddr, AIC31_P0_REG65, 0x7F); /* is off */

/* DACL1 connected to LINE1 LOUT */

CodecRegWrite(baseAddr, AIC31_P0_REG82, 0x80); /* DAC_L1 is connected */

CodecRegWrite(baseAddr, AIC31_P0_REG86, 0x09); /* unmuted/power on */

/* DACR1 connected to LINE1 ROUT */

CodecRegWrite(baseAddr, AIC31_P0_REG92, 0x00); /* DAC_R1 is not connected */

CodecRegWrite(baseAddr, AIC31_P0_REG93, 0x00); /* muted/power off */

/* unmute the DAC */

CodecRegWrite(baseAddr, AIC31_P0_REG43, 0x00);/* left channel is mute */

CodecRegWrite(baseAddr, AIC31_P0_REG44, 0x80);

/* McASP configuration: */

/* reset MCasp (GBLCTL) */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_RGBLCTL)= 0;

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XGBLCTL) = 0;

/* Receiver configuration */

/* Configure Mask */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_RMASK) = 0x0000FFFF;

/* Configure format of receive section */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_RFMT) = 0x0001807C; /* 1 bit delay/MSB/slot size 16bit/read from Periph */

/* Clocks control */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_AFSRCTL) = 0x00000112; /* I2S mode/ internal frame clock/ rising edge */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_ACLKRCTL) = 0x000000AF; /* rising edge/ Divide by 16 */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_AHCLKRCTL) = 0x00000000; /* Divide by 1/ clock source from AUCLKX */

/* Set Active Slots */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_RTDM) = 0x00000003;

/* Configure receiver clock check circuit */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_RCLKCHK) = 0x00FF0008;

/* Transmitter configuration */

/* Configure Mask */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XMASK) = 0x0000FFFF;

/* Configure format of transmitt section */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XFMT) = 0x0001807C; /* 1 bit delay/MSB/slot size 16bit/read from Periph */

/* Clocks control */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_AFSXCTL) = 0x00000112; /* I2S mode/ internal frame clock/ rising edge */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_ACLKXCTL) = 0x000000AF;

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_AHCLKXCTL) = 0x00000000;

/* Set Active Slots */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XTDM) = 0x00000003;

/* Configure transmitter clock check circuit */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XCLKCHK) = 0x00FF0008;

/* Set serializers numbers */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_SRCTL(13u)) = 0x0000000D; /* Set serializer13 as transmitter */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_SRCTL(14u)) = 0x0000000E; /* Set serializer13 as receiver */

/* Configure pins */

/* Set McASP as GPIO */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_PFUNC) = 0;

/* Set Pins Direction */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_PDIR) = 0x14002000;

/* Enable DIT mode transmission */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_DITCTL) = 0x00000000;

/* Enable DLB mode transmission */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_DLBCTL) = 0x00000000;

/* Configure McAsp Mute */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_AMUTE) = 0x00000000; /* if clk clock failed set mute */

/* Start McAsp : */

/* Transmit high-frequency clock divider is running */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XGBLCTL) |= 0x00000200; /* XHCLKRST */

/* Wait untill it's working */

while(!(HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XGBLCTL)&(0x00000200)));

/* Receive high-frequency clock divider is running */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_RGBLCTL) |= 0x00000002; /* RHCLKRST */

/* Wait untill it's working */

while(!(HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_RGBLCTL)&(0x00000002)));

/* Transmit clock divider is running*/

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XGBLCTL) |= 0x00000100; /* XCLKRST */

/* Wait untill it's working */

while(!(HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XGBLCTL)&&0x00000100));

/* Receive clock divider is running*/

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_RGBLCTL) |= 0x00000001; /* RCLKRST */

/* Wait untill it's working */

while(!(HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_RGBLCTL)&&0x00000001));

/* Set Interrupts */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_RINTCTL) = 0x00000020; /* Data ready Interrupt */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XINTCTL) = 0x00000020; /* Transmit Data ready/ Sync Frame Start Interrupts */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_RSTAT) = 0x0000FFFF; /* Clear Receiver Status Register */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XSTAT) = 0x0000FFFF; /* Clear Transmitter Status Register */

/* Transmit serializers are active */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XGBLCTL) |= 0x00000400; /* XSRLCR */

/* Wait untill it's working */

while(!(HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XGBLCTL)&(0x00000400)));

/* Receive serializers are active */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_RGBLCTL) |= 0x00000004; /* RSRLCR */

/* Wait untill it's working */

while(!(HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_RGBLCTL)&(0x00000004)));

/* Send 0, so that no underrun occurs after releasing the staet machine */

McASPTxBufWrite(SOC_MCASP_0_CTRL_REGS, MCASP_XSER_TX, 0);

/* Transmit state machine is released from reset */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XGBLCTL) |= 0x00000800; /* XSMRST */

/* Wait untill it's working */

while(!(HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XGBLCTL)&(0x00000800)));

/* Receive state machine is released from reset */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_RGBLCTL) |= 0x00000008; /* RSMRST */

/* Wait untill it's working */

while(!(HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_RGBLCTL)&(0x00000008)));

/* Transmit frame sync generator is active */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XGBLCTL) |= 0x00001000; /* XFRST */

/* Wait untill it's working */

while(!(HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XGBLCTL)&(0x00001000)));

/* Receive frame sync generator is active */

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_RGBLCTL) |= 0x00000010; /* RFRST */

/* Wait untill it's working */

while(!(HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_RGBLCTL)&(0x00000010)));

while(!(HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XSTAT)&0x20));

McASPTxBufWrite(SOC_MCASP_0_CTRL_REGS, MCASP_XSER_TX, 0);