Other Parts Discussed in Thread: ALP

Dear TI Experts,

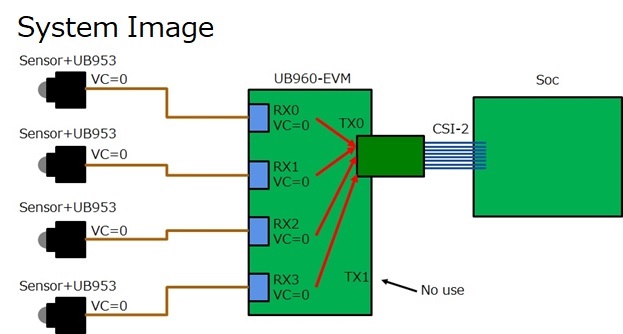

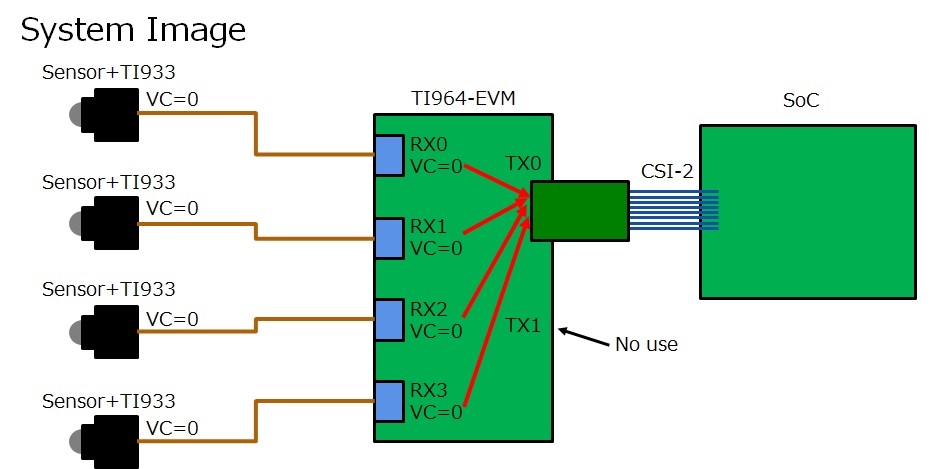

We are examining the connection 4 cameras in Line-concatenated forwarding of UB964.

(Refer System image)

There is no problem if there are 3 cameras connections,

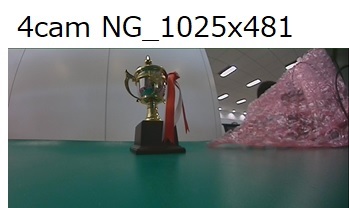

but if there are 4 cameras connections, the picture does not appear correctly.

(Refer Get image. 3cameras connections:3843x481 4cameras connections,:1025x481)

We have exceeded the Line length specification.

Please tell me the limit of Line Length at Line-concatenated forwarding.

Our environment is below.

・4 cameras connect (1280x480,YUV422,216Mbps/Lane)

・Serializer is UB933

・UB964 CSI output is 1600Mbps/Lane setting

・Output port is CSI-TX0

・VC:0,DT:1F

・Frame Sync mode (Line-concatenated forwarding)

Thank you and best regards,