Hi Team,

I posted thread 5 month ago, and got an answer as below but it doesn't work in my customer's board. May I double check if these commands are really enough for channel switching using MDIO?

Could you send me a EVM macro to connect ChA HS to ChB LS in 9 hours? I have a EVM now so I can check it tomorrow morning.

I have to have a meeting with the customer to clarify this issue tomorrow afternoon (I might need to highly escalate this if we will be not able to solve this issue within this weekend)

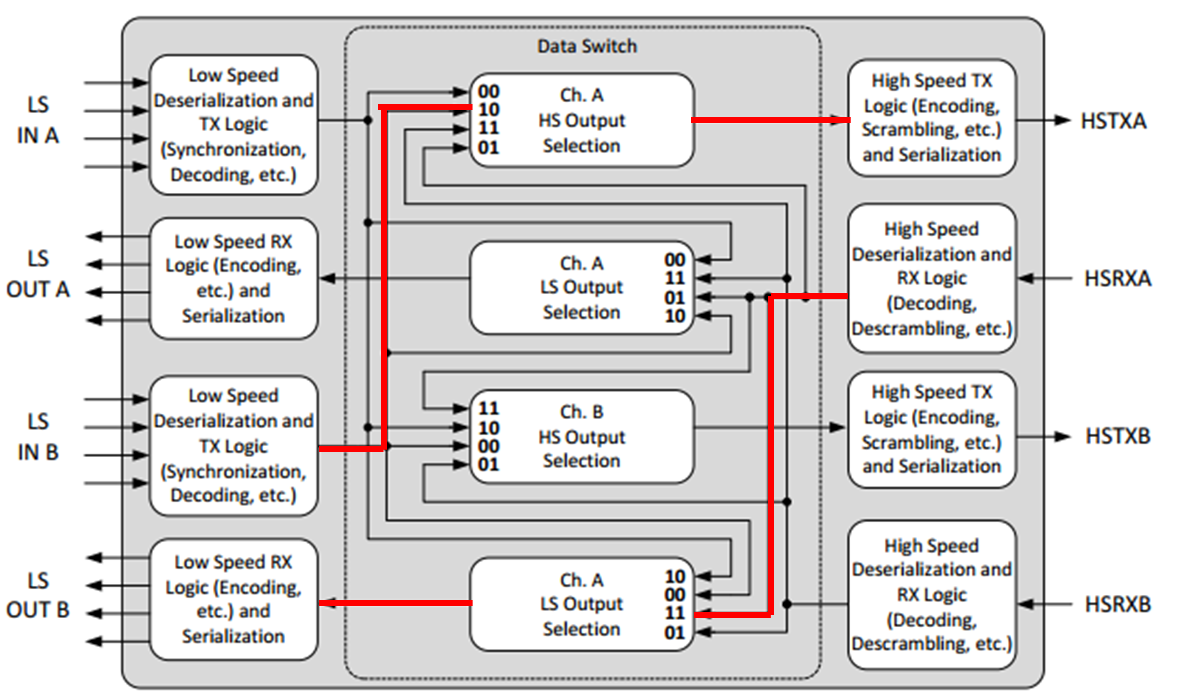

//Setting for DATA Switch TX (LSB=>HSA direction)

To Ch-A phy address;

Write 1'b0 to 0x1E.0017 bit 12 (DST_PIN_SW_EN)

Write 2’b10 to 0x1E.0018 bits 15:14 (DST_DATA_SRC_SEL[1:0]) //Selects data from Low Speed CHB to High Speed CHA

//Setting for DATA Switch RX (HS=>LS direction)

To Ch-A Ch-B phy address;

Write 1'b0 to 0x1E.0019 bit 12 (DSR_PIN_SW_EN)

Write 2’b11 to 0x1E.001A bits 15:14 (DSR_DATA_SRC_SEL[1:0])

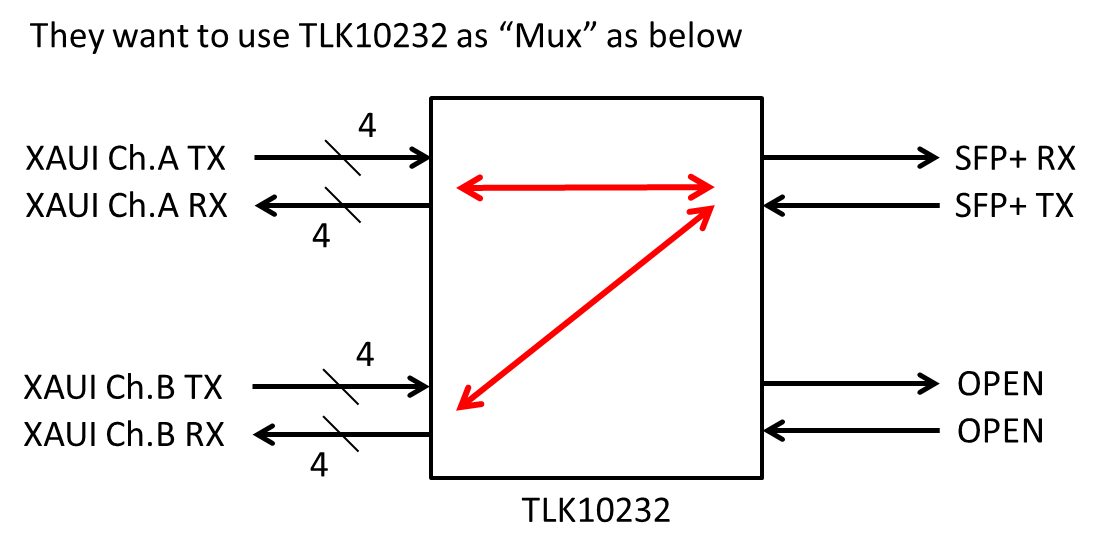

My customer would like to switch LSs to chA HS as below. And they will use 10G-KR mode. They plan to connect SFP+ module at ChA HS so they send the commend below prior to the command for switching above.

PA:0b00000 DA:0b11110(0x1E) REG_AD:0x0000 WR_DATA:0x8610

PA:0b00000 DA:0b11110(0x1E) REG_AD:0x001D WR_DATA:0x0000

PA:0b00000 DA:0b00111(0x07) REG_AD:0x0000 WR_DATA:0x2000

PA:0b00000 DA:0b00001(0x01) REG_AD:0x0096 WR_DATA:0x0000

PA:0b00000 DA:0b11110(0x1E) REG_AD:0x8020 WR_DATA:0x03FF

PA:0b00000 DA:0b11110(0x1E) REG_AD:0x0004 WR_DATA:0xD500

PA:0b00000 DA:0b11110(0x1E) REG_AD:0x000E WR_DATA:0x0008

PA:0b00001 DA:0b11110(0x1E) REG_AD:0x001D WR_DATA:0x0000

PA:0b00001 DA:0b00111(0x07) REG_AD:0x0000 WR_DATA:0x2000

PA:0b00001 DA:0b00001(0x01) REG_AD:0x0096 WR_DATA:0x0000

PA:0b00001 DA:0b11110(0x1E) REG_AD:0x8020 WR_DATA:0x03FF

PA:0b00001 DA:0b11110(0x1E) REG_AD:0x0004 WR_DATA:0xD500

PA:0b00001 DA:0b11110(0x1E) REG_AD:0x000E WR_DATA:0x0008

After sending these commands, they could not read DATA_SWITCH_STATUS register(The read values are always 0x0000).

Regards,

Takashi Onawa