Tool/software: Code Composer Studio

Hi all,

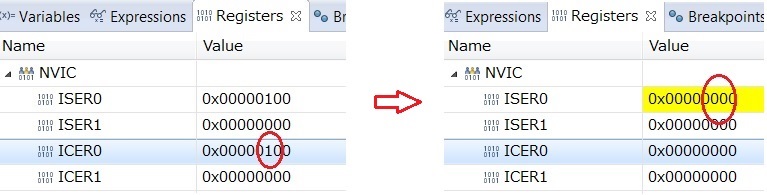

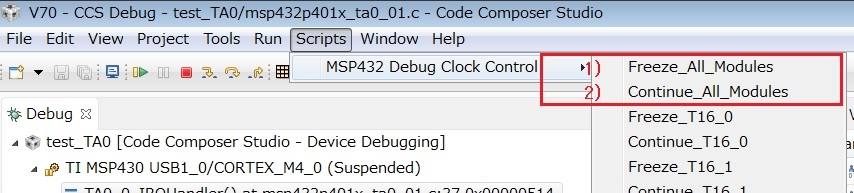

I've been in the process of making edits to my current MSP432 code for our PCB. This code ran perfectly fine on the red Eval board. However, on the MSP-FET we use for our PCB designs, when I step through the code, immediately after I pass over the line to enable either of the TimerA interrupts the code will immediately step into the ISR for the TimerA and will go in and out of it forever. When I run to the next breakpoint, it will do that no problem, but go back into that interrupt when I step in again.

I've tried to solve this problem with multiple computers, MSP-FET's, workspaces, and using CCSv6 vs. CCSv7 but I've concluded this is an error with the MSP-FET debugger. The code works as it should if I run to breakpoints, or if I run it on the Eval board that has the XDS110 debugger, but as of now, I cannot use the MSP-FET's to step through projects with the TimerA module using ISR's.

I can get around this for now using the Systick module which isn't giving me these problems, but I'd prefer to use the TimerA module with ISR's in the future.

Thanks,