Other Parts Discussed in Thread: UNIFLASH, SEGGER

Tool/software: Code Composer Studio

I have 50 boards with the TM4C1294NCPDT uP, running at 24MHz. On 10 boards the JTAG will not work, with same setup, if I plug the JTAG into a "good" board, same setup, same hardware, same session, it programs just fine. We did not put in the RBIAS resistor on any of the boards, again 40 will connect and program through the JTAG.

I am about to fab a production qty and have to get this resolved.

RBIAS and JTAG post:

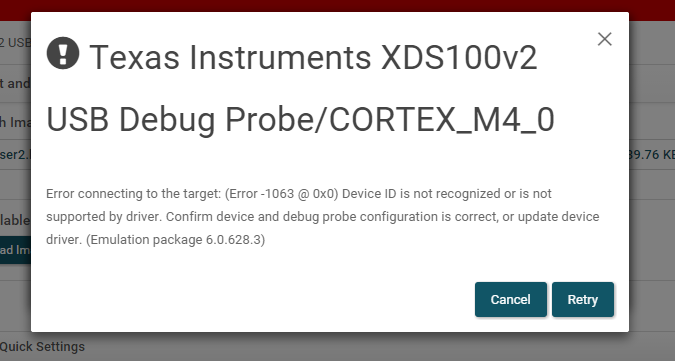

I use either the Launchpad eval board or the XDS100v2, both work fine and multiple times on good boards. I have tried Uniflash and LMFlash, both work. I took 2 boards, put in RBIAS and I still get the same error. I tried and finished Unlock; still dead.

If an attempt to program the uP w/o RBIAS, is it fried?

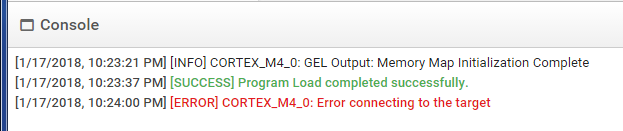

Output from Uniflash: