Hi all,

The datasheet of TPS65217 details the functionality of PB_IN pin of the TPS65217 as below :

- Power-up the device from OFF or SLEEP mode upon detecting a falling edge on PB_IN.

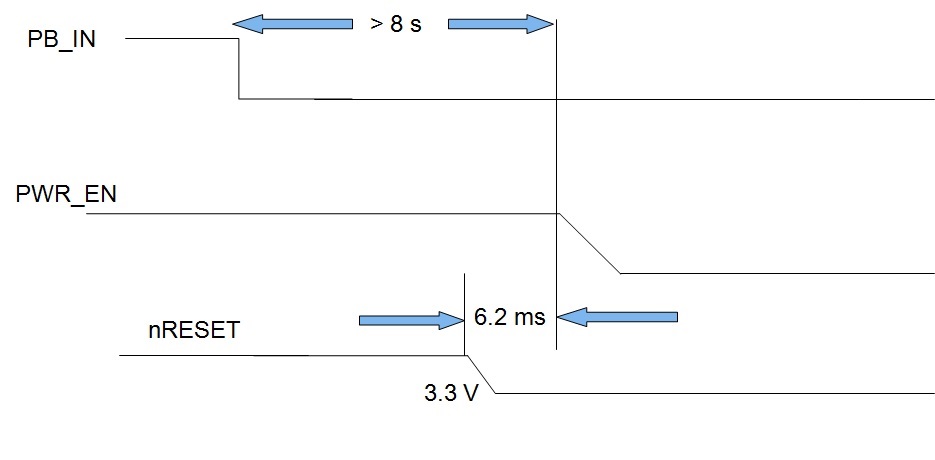

- Power cycle the device when PB_IN is held low for > 8 s.

We assume that the power cycle refers to the PMIC starting a new power - up sequence. This will result in rebooting of the system.

We tried this using Beagle bone black (by pressing Switch S1 for 8 secs) & the board powered off rather than rebooting.

Can somebody please clarify the functionality of PB_IN pin of TPS65217 ? Is the functionality is power cycle or power off ?

Thanks,

Suresha N S