PCIe (Peripheral Component Interconnect Express) 仕様は 20 年近くにわたって、民生用と産業用両方のアプリケーションで相互接続の規格として使用され、プロセッサや SSD (ソリッド・ステート・ドライブ)、その他の技術やエンド・ポイントの相互間で高速インターフェイスを実現してきました。この規格が広く採用されている背景には、いくつかの要因があります。

- PCIe のエコシステムは特定の企業の独自仕様ではなく、多くの設計者が快適に取り組めるオープン形式のリソースから構成されます。

- PCIe の通信プロトコルは、さまざまなシリアル・ペリフェラル・インターフェイスに対応しており、レイテンシ (待ち時間) が非常に短く、帯域幅のスケーラビリティが優れています。PCIe の 1 レーンあたりのスループットは、世代が 1 つ進むごとに 2 倍の速度向上を継続しており、異なるリンク幅にスケーリングできるフレキシビリティも備えています。たとえば、16 レーン (x16) の PCIe 5.0 構成全体のスループットは 64Gbps ですが、これを 4 組の 4 レーン (x4) 構成に分割して各組で 16Gbps のスループットを確保することも、または 16 組の 1 レーン (x1) 構成に分割して各組で 4Gbps のスループットを確保することもできます。このようなフレキシビリティにより、1 レーンの通信から 16 レーン構成まで、多様な種類のアプリケーションで PCIe を採用することが可能です。

現在では、データの処理を必要とするほぼすべての技術において、より高速なデータ・レートが求められているため、設計者は PCIe 仕様を満たすために複雑な熱設計や信号の劣化など、シグナル・インテグリティに関するいくつかの課題を克服する必要があります。ビアを使用した場合や、プリント基板 (PCB) の材質、コネクタやケーブルの特性などに問題がある場合、データのマージンに大きな影響が及び、受信したデータにエラーが生じます。そのような場合、リドライバのようなシグナル・コンディショナを PCIe リンクに追加すると、エラーがなく、より信頼性の高いデータ転送を実現できるようになります。

この記事では、PCIe リドライバに関する 3 つのよくある誤解について解説します。

誤解その 1:エンド・ポイントの種類が多岐にわたるため、PCIe リドライバの相互運用性には課題がある

PCI-SIG (Peripheral Component Interconnect Special Interest Group:PCI を策定する業界団体) は、PCIe のデータ転送に関する標準化仕様を管理しています。PCI-SIG には、高速かつ相互運用可能な製品の開発に特化した 1,000 社以上の企業メンバーが参加し、いくつかの規格準拠作業部会を主宰しており、各社は自社製品が PCIe 仕様の非常に重要ないくつかの要素を満たしているかどうかを検証できます。このプロセスを通じて、他社のルート・コンプレックス (PCIe 階層の最上位にあるコントローラ) やエンド・ポイントとの間で包括的な相互運用性テストを実施するので、各社は自社の PCIe シグナル・コンディショナの能力全体を把握することができます。たとえば、TIの『DS320PR810』リドライバは、複数のルート・コンプレックスやエンド・ポイントとの組み合わせを使用して、PCI-SIG の規格準拠テストに合格しました。社内テストでも PCIe 仕様の重要な要素を検証することはできますが、PCI-SIG の規格準拠テストに合格すれば、製品の能力に関してさらに確実な根拠を確立できます。

誤解その 2:PCIe リドライバの適切な設定を見つけるには、手動で多くのプロセスを実施する必要がある

リニア・リドライバは、デバイスの物理層またはポートに関する構成や初期化を必要としないので、設計はシンプルです。適切な CTLE (continuous time linear equalization:連続時間リニア・イコライザ) 設定を見つけるために、CTLE とゲインに関する多様な設定すべてを手動で試す必要はありません。ハードウェア設計者が最適な設定を迅速に見つけるのに役立つ、複数のツールと手法が存在しています。

設計者は IBIS-AMI (Input/Output Buffer Information Specification algorithmic modeling interface:入出力バッファ情報の仕様を取り扱うアルゴリズム形式モデル化インターフェイス) を活用して、リドライバに関するチャネル入力前とチャネル出力後の各効果をシミュレートしたり、実際のリンク特性に近いアイ・パターンを求めたりすることができます。シミュレーション・モデルは、トランスミッタとレシーバを含めたチャネル全体の詳細なアナログの電気的挙動を表します。また、このシミュレーションでは、CTLE の設定全体を一括テストし、最適な設定を見つけることもできます。

リドライバを調整する別の方法は、ネットワーク・アナライザを使用して基本周波数で送信チャネルの挿入損失を測定し、測定された挿入損失を補償する CTLE 設定を見つけることです。たとえば、PCIe 5.0 ソリューションを設計する場合、16GHz を使用してリドライバの入力側で挿入損失を測定することが考えられます。仮に挿入損失が 10dB である場合、この挿入損失を補償するために +10dB のゲインを確保することが CTLE 設定の出発点になります。一般的に、CTLE の適切な初期設定をすばやく見つけ、シグナル・パス内で最善のマージンを確保するために、この調整方法が役に立ちます。

誤解その 3:PCIe リドライバはリンクの中間に配置する必要があるので、設計のフレキシビリティが低下する

システム内に存在するさまざまな要因が、信号の劣化を招く可能性があります。PCB のさまざまな材質とパターン長、信号の取り回しに使用するビアの数、コネクタの多様な特性などが原因で、リドライバのチャネル入力前損失とチャネル出力後損失が変化する可能性があります。リドライバを配置する位置は、システムの損失プロファイルによって異なります。最善のソリューションを実現するために、必ずしもリンクの中間に配置する必要があるとは限りません。チャネル数が異なる状況ごとに、異なる構成を採用したリドライバを使用し、設計で最大のフレキシビリティを確保することができます。レーン構成ではなく、単方向の構成を使用する場合、設計者はエンド・ポイントのできるだけ近くにリドライバを配置することで、到達距離をさらに延長できます。

PCIe スロット数に制約があるアプリケーションでも、いくつかのリドライバはマルチプレクシング構成機能を内蔵しているので、複数のルート・コンプレックスと複数のエンド・ポイントをサポートできます。たとえは、TIのリニア・リドライバである『SN75LVPE5412』を使用する場合、中央演算装置 (CPU) のような 1 個のルート・コンプレックスが、2 台の SSD (ソリッド・ステート・ドライブ) と通信する構成を採用し、SEL ピンを活用して 2 台のエンド・ポイント間でデータ取り出しを多重化することもできます。スペースの制約が厳しい PC アプリケーションの場合、この構成は一般的です。リドライバには、小型フォーム・ファクタかつ低消費電力という特長があるので、通信の観点でスペース制約に対処できるだけでなく、ヒートシンクや大型の放熱パッドが不要になるため、ボードの高さに関する要件を簡単に満たすことができます。

加えて、リドライバのレイテンシは数百 ps (ピコ秒) という非常に小さい値なので、ルート・コンプレックスとエンド・ポイントの間で遅延時間を考慮したり待機したりする必要なしに、処理能力を最大限に活用して、より多くのタスクを効率的に実行することができます。シグナル・コンディショナに起因するレイテンシの制限がないことで、処理能力が向上し、設計のフレキシビリティがいっそう高まります。

実際のアプリケーションでリドライバを使用した例を紹介します。

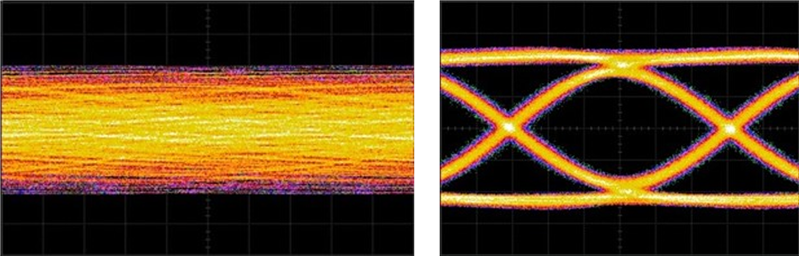

図 1a では、チャネル入力前損失が非常に大きく、アイ・パターンの開口面積が小さくなっています。これは、ルート・コンプレックスまたはエンド・ポイントが、意味のあるデータを取得できないことを意味しています。この場合、1 つの選択肢として、PCB をアップグレードし、損失が非常に小さい材質を使用することで、開口面積が大きくなる可能性がありますが、コストは上昇します。もう 1 つの選択肢は、リンクにリドライバを追加することです。図 1b では、リンクにリドライバを追加したことで、アイ・パターンの開口面積が大きくなり、十分な信号マージンを確保して信号品質を改善できたことを示しています。

(a) (b)

図 1:PCIe 4.0 リドライバの (a) チャネル入力前信号と (b) チャネル出力後信号

まとめ

PCIe リドライバはプロトコルに依存しないため、データ・レートの要件内で、CXL、SAS、SATA など、PCIe ベースのハードウェアを使用する任意のプロトコルをサポートできます。リドライバは複数のプロトコルをサポートしているので、シグナル・コンディショニングを必要とする多様な高速アプリケーションで使用できます。ボード上に存在する多様なリンクすべてにわたって信号品質全体を改善するために、損失が非常に小さい PCB 材質を使用することもできますが、この場合は全体のコストが上昇します。代わりに、システム内でより多くのマージンを必要とする少数のリンクのみに、必要に応じてリドライバを追加することができます。リドライバを追加する方法では、PCB 全体の材質をアップグレードする必要がないため、コストをさらに節減し、信号品質を向上させるシンプルな選択肢として考慮できます。

参考情報:

信号劣化の課題に関する詳細については、TIのPCIe シグナル・コンディショニング・ソリューションをご覧ください。

※すべての登録商標および商標はそれぞれの所有者に帰属します。

※上記の記事はこちらの技術記事(2022年10月24日)より翻訳転載されました。

※ご質問はE2E Support Forumにお願い致します。