Hi,

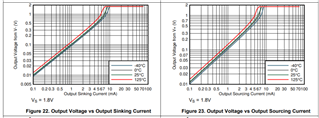

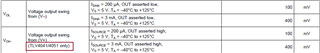

I am designing in the TLV4041R5DBVR push-pull part (I would prefer Open Drain, but unfortunately, there is no Open Drain part in a package larger than tiny DSBGA). I need to connect the output of this comparator to the LVCMOS18 input of FPGA (both the comparator and FPGA Bank use 1.8V supply). The only info on VOL/VOH for this comparator in the data sheet is this:

I have no control over Isource (what is it by the way?), and my Vs=1.8V. My feeling is the FPGA pin will switch OK, as FPGA's VILmax=0.63V and VIHmin=1.17V, but how do I come up with correct numbers for VOL/VOH here? the FPGA pin leakage current is <|15|uA.