Other Parts Discussed in Thread: LM358, REF4132

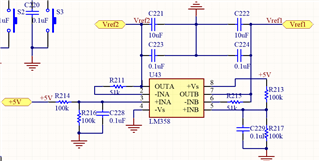

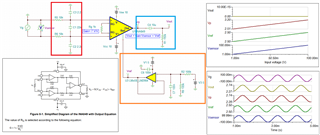

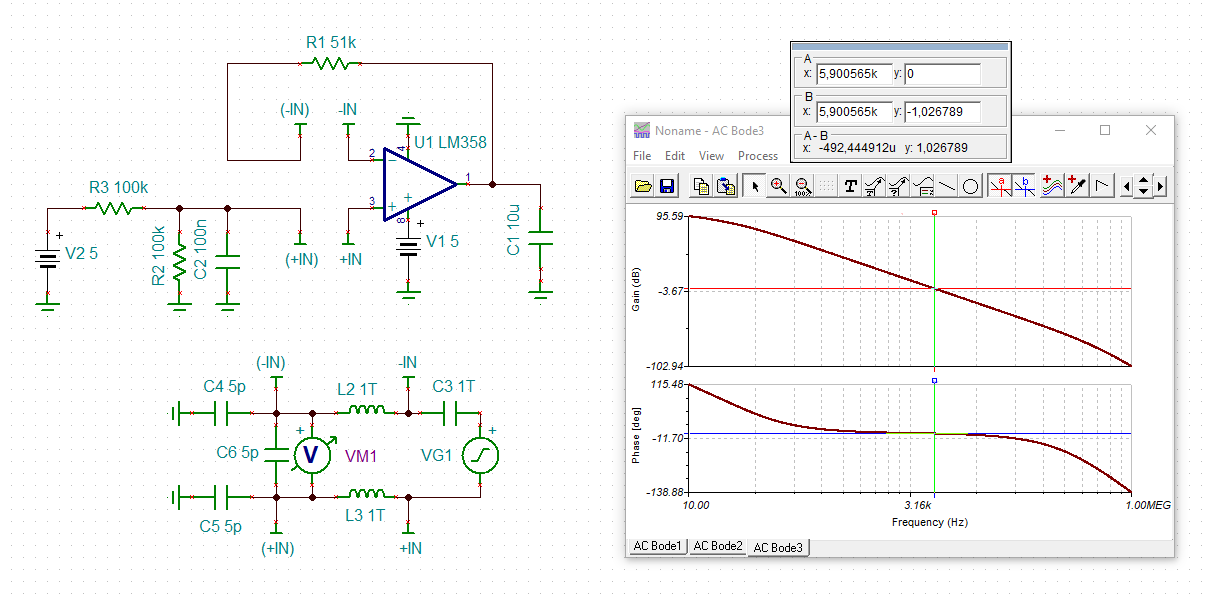

With Vref 2.5V, the output should normally fluctuate up and down with 2.5V as the center.

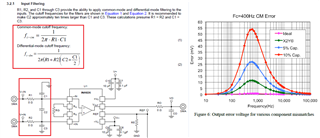

Now the bad problem: when the input is below 4mV, the output is centered at 2.5V,

The larger the input amplitude is, the more obvious the output shift is. When the input reaches 10mV, the shift is about 1V.

Please help analyze the possible reasons and design instructions for related problems.

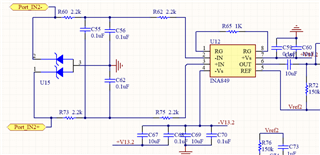

Input differential mode Common mode and power supply are within Diamond Plot safe range

power supply :+/-10V