Other Parts Discussed in Thread: TLV313, , TINA-TI

Dear Experts,

my application requires a high input impedance. Therefore I am using 2 x TLV313 OpAmps as unity-gain buffers for my ADS1296. They also provide an adequate common-mode output voltage (2.5 V) for my ADC. My signal of interest is 0 - 10 kHz. The ADCs modulator frequency (as I understand is the actual sampling frequency) is, depending on the mode, 512 kHz or 256 kHz, which puts it's Nyquist frequency to 256 kHz or 128 kHz. At and above the Nyquist frequency I would want to have significant attenuation of my input signal to not have components above that frequency folding back into my spectrum of interest.

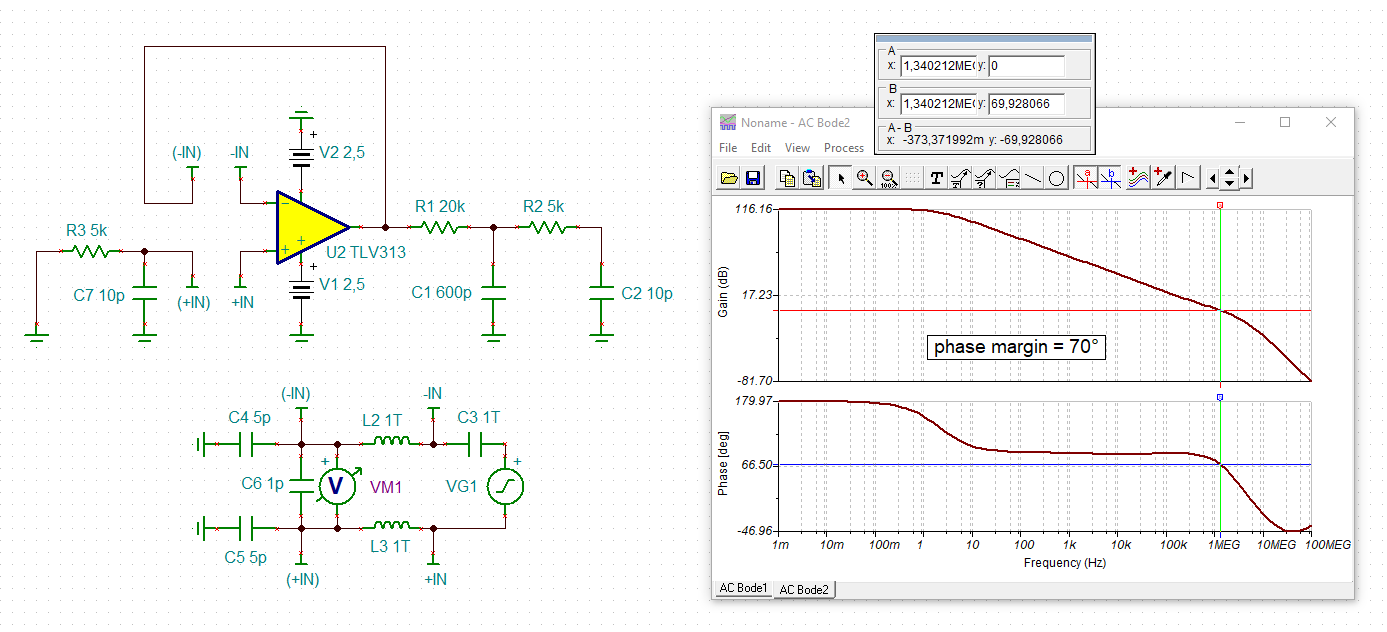

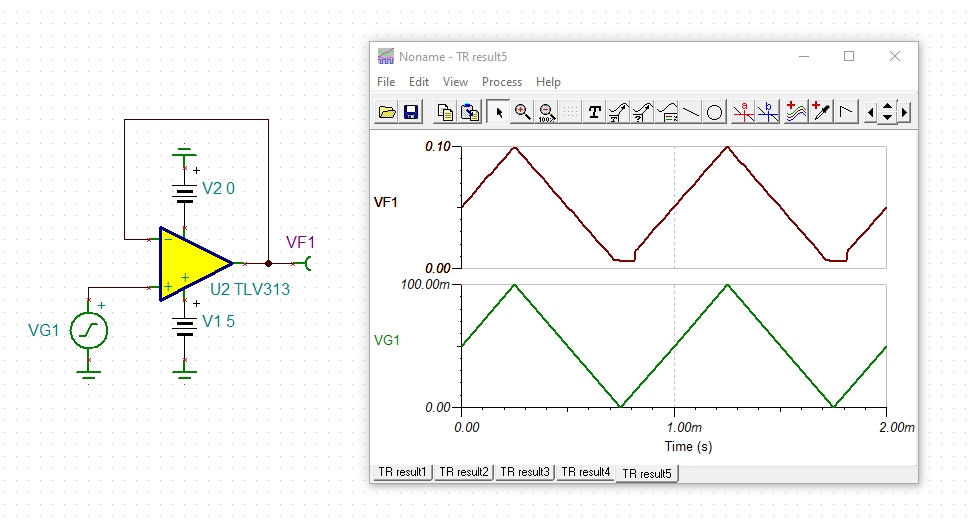

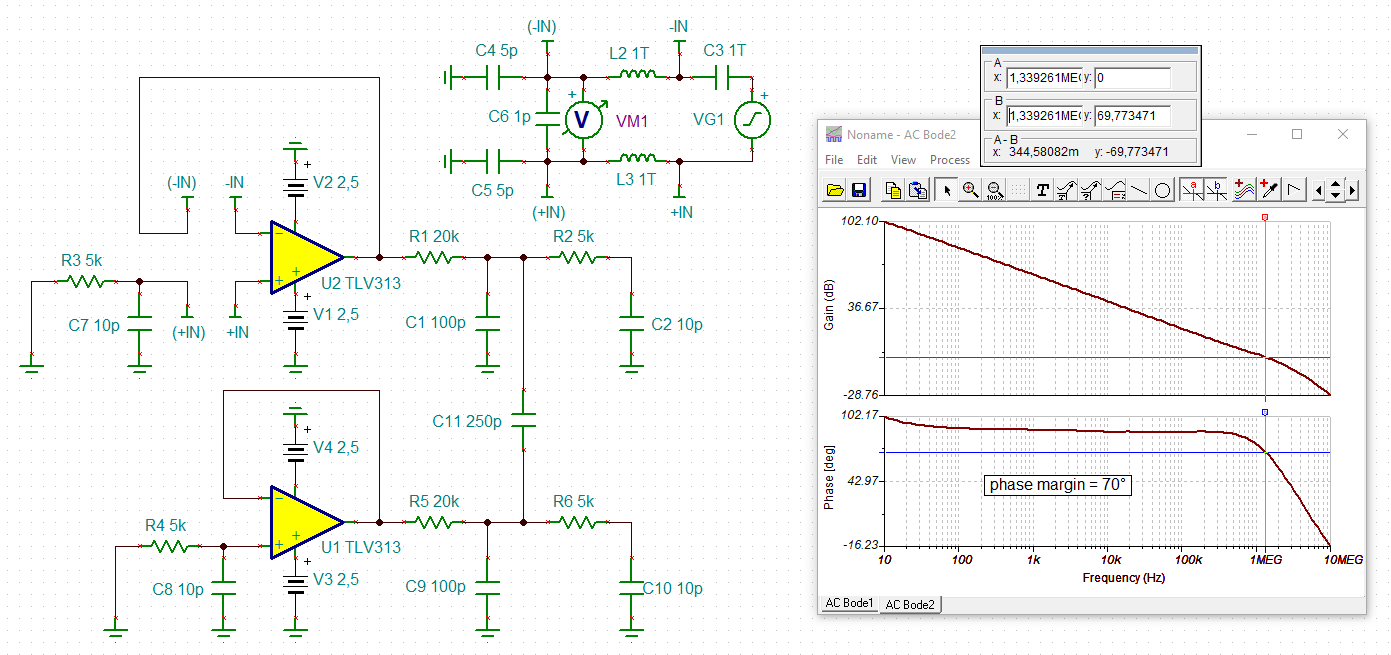

However, I cannot build a reasonable (RC) low-pass at the input of the TLV313, because the capacitor to ground would decrease my input impedance, which I need. E.g., the TLV313 has an input capacitance of 1 pF and an RC low pass with a cutoff frequency of 25 kHz for example, in combination with a 10 kOhm series input resistance of the TLV313 (recommended to decrease input current at a reasonable noise level), would already require a capacitance to GND of 630 pF (and hence strongly decreasing my input impedance). I am willing to build a strong filter (e.g., third order Chebyshev) at my TLV313 output stage. However, I only find that the TLV313 can drive up to 1 nF of a purely capacitive load (TLV313 OpAmps, page 17). How do I know if this works with a more complicated filter inlcuding uH inducatances, uF capacitances and some kOhms?

This is my current design (limited attenuation at 128 kHz --> around 20 dB or so):

So my questions are basically manifold:.

1. How large do I need to filter/attenuate my signals at the Nyquist frequency already?

2. What is the usual/good practice to employ a strong filter after unity-gain buffers?

3. How do I know if my TLV313 will function with a complicated mix of R-L-C in case I use a higher order (Chebyshev) filter? What are the resistance limits for my TLV output/my ADC input? I read with another ADC from Analog that the series resistance towards the ADC cannot be larger than 2 kOhms for example, for the ADC to be able to buffer / get enough current. For this ADC I don't find this information.

4. At a data rate of 32 kHz my noise level is quite high: 521 µV_RMS and 5388 µV_pp (5.4 mV_pp). What is the minimum input signal (sine wave) I require to still be able to have a proper signal? I searched a bit for SNR on different applications but only found very general statements. What should the peak to peak voltage of my input signal be as a minimum?

5. From the ADS1296 datasheets it reads that the gain does influence my noise. But if my noise is halve the value at twice the gain for example, from my thinking this would not give me much, as I would need to decrease my input signal strength as well. So the SNR is basically the same (e.g.: 2 V input signal and 500 µV_RMS noise at Gain = 1; is equally reasonable than 1 V input signal and 250 µV_RMS noise at Gain = 2). Am I missing something?

Any input is highly appreciated!

Best wishes and thank you! Rene