Other Parts Discussed in Thread: OPA593, TINA-TI, OPA551

Hi ,

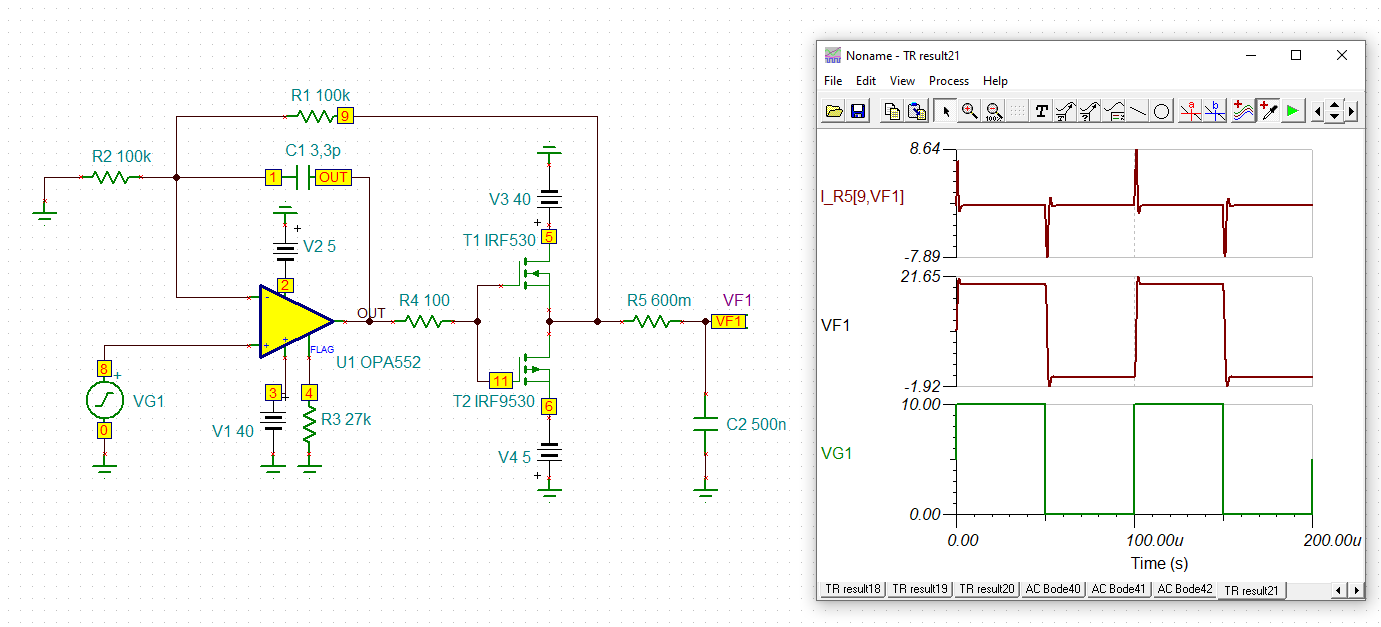

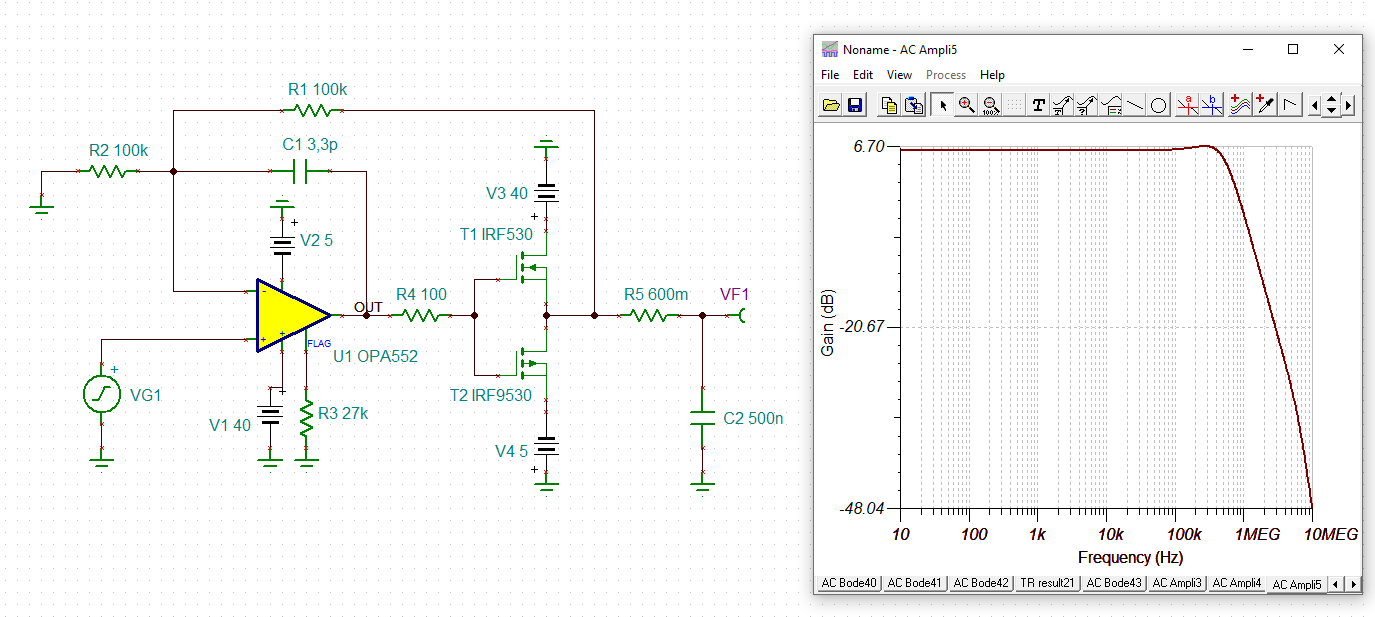

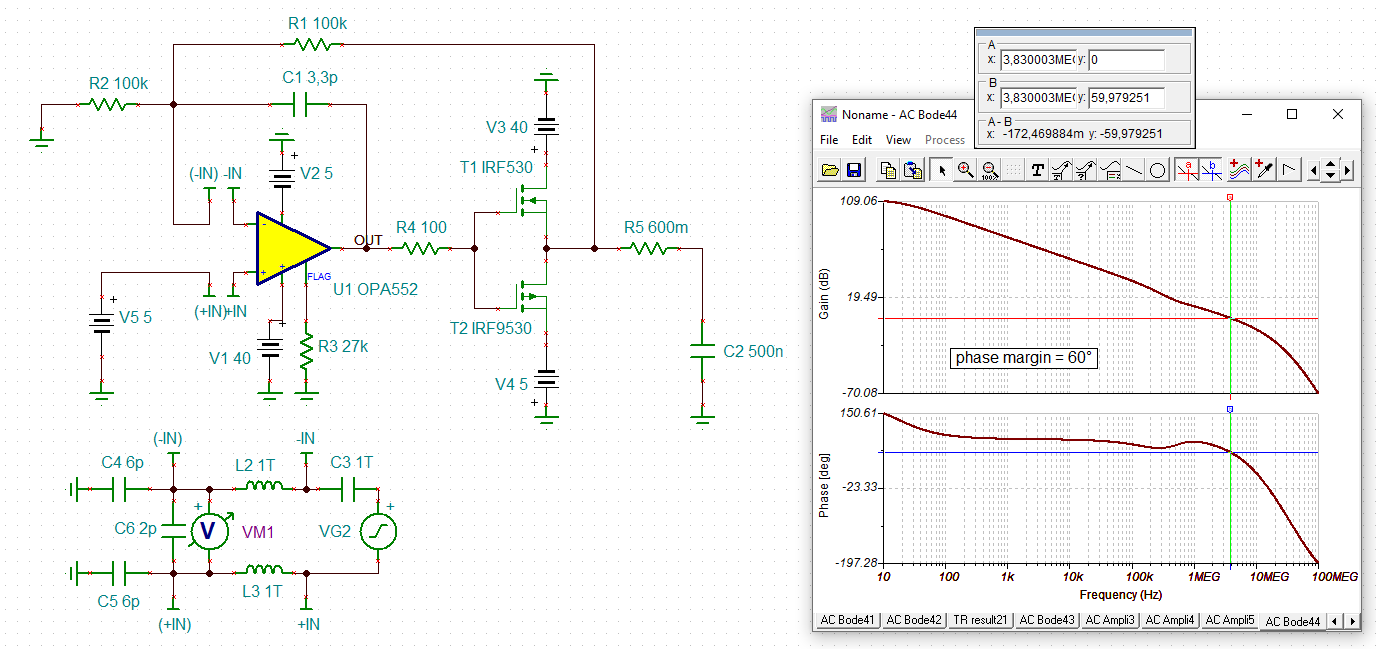

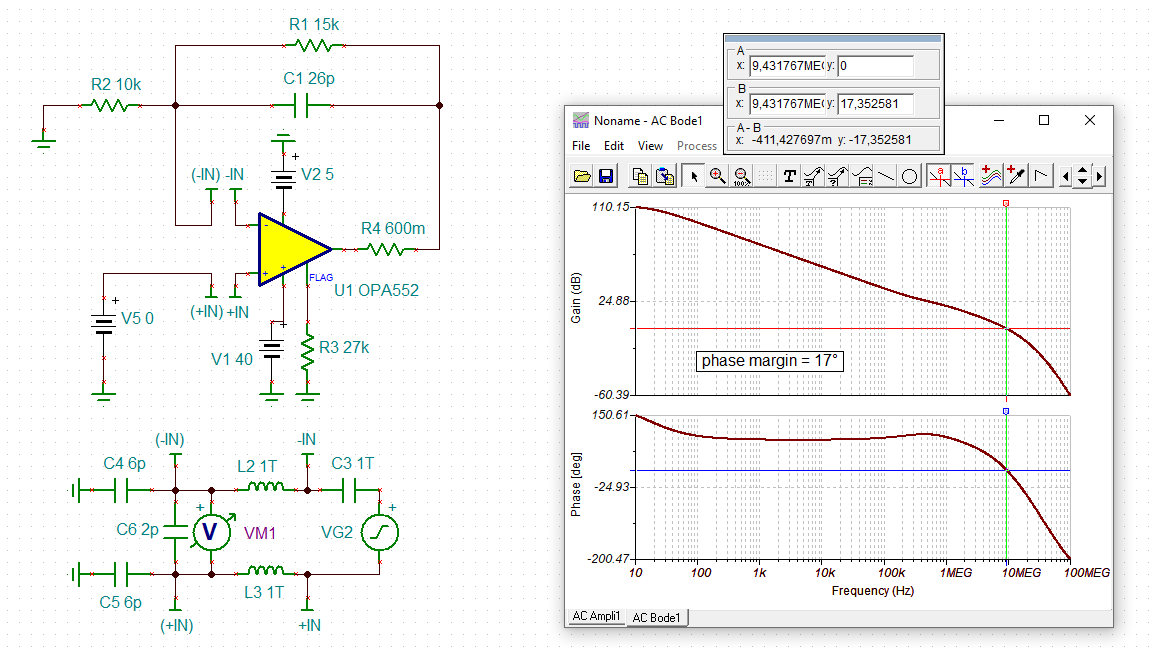

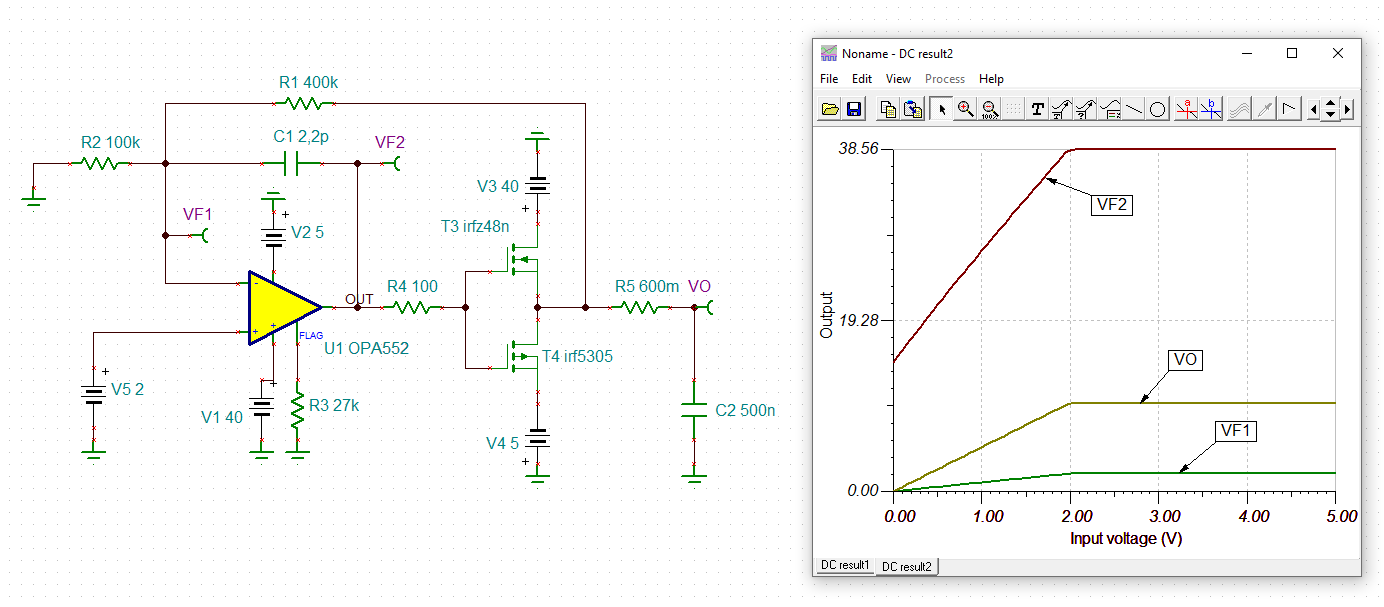

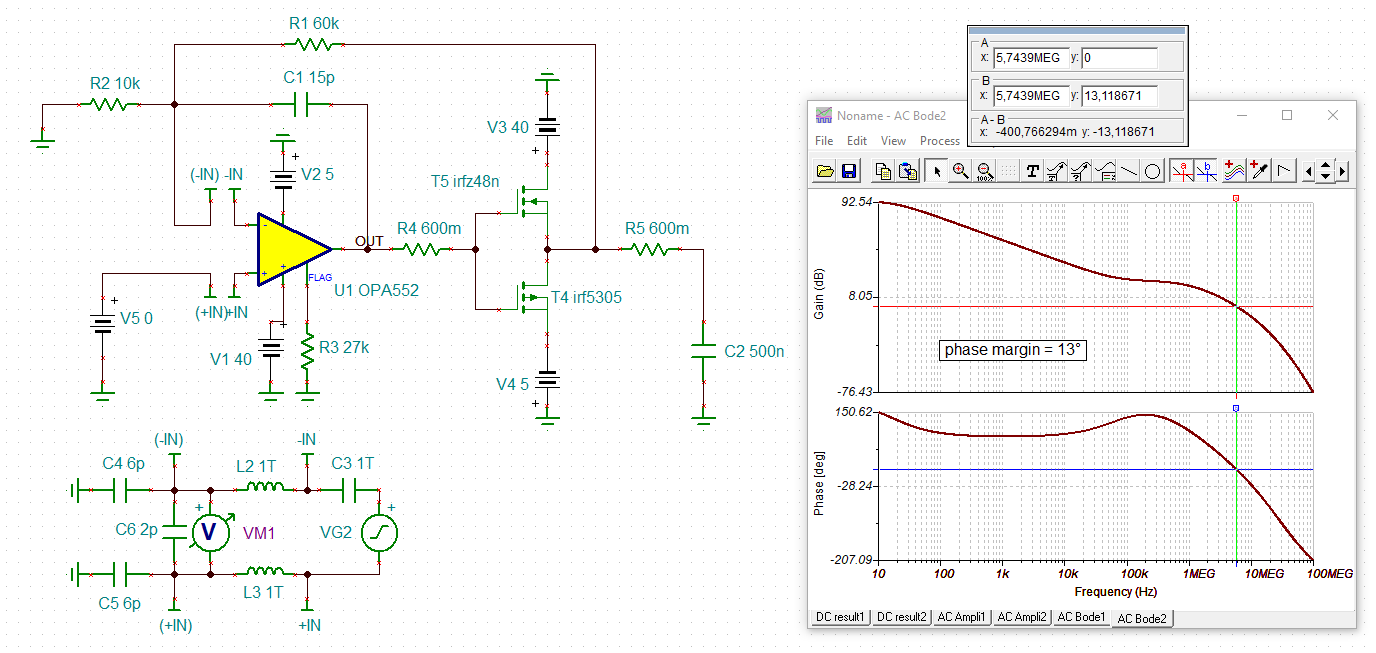

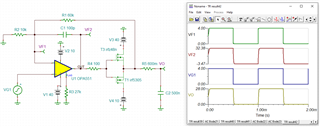

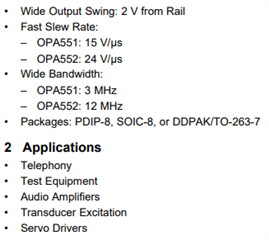

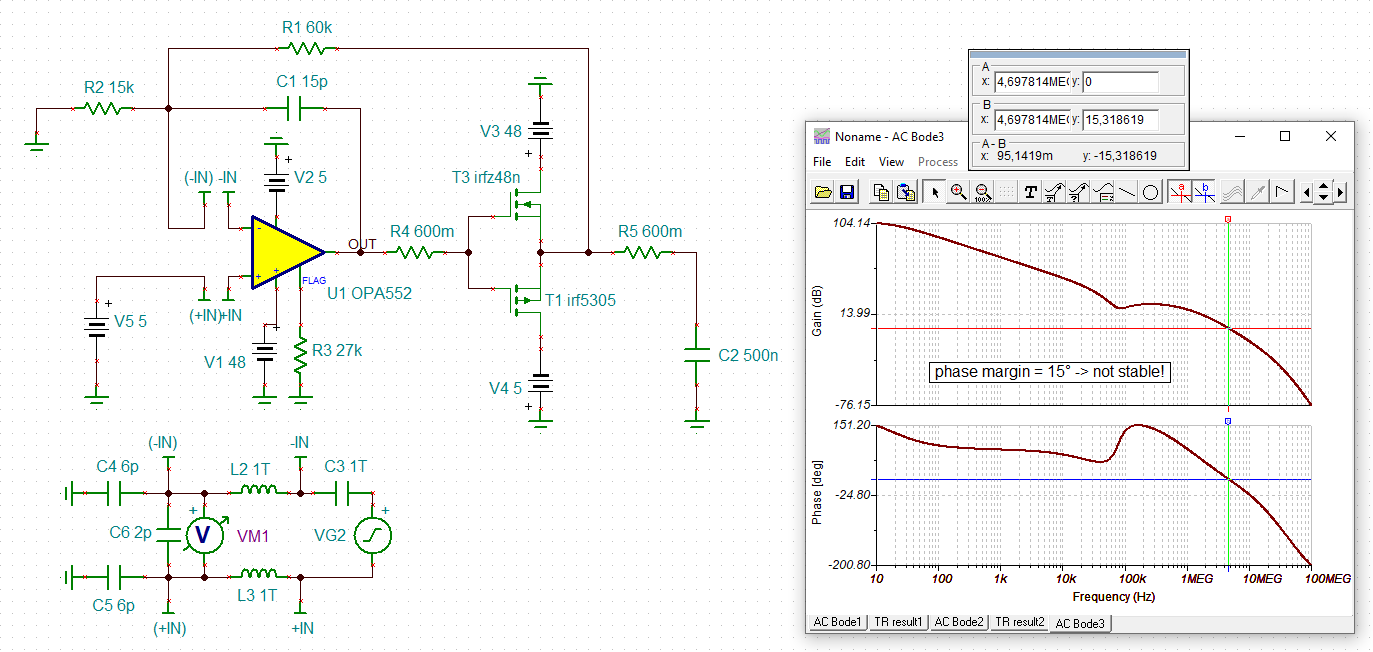

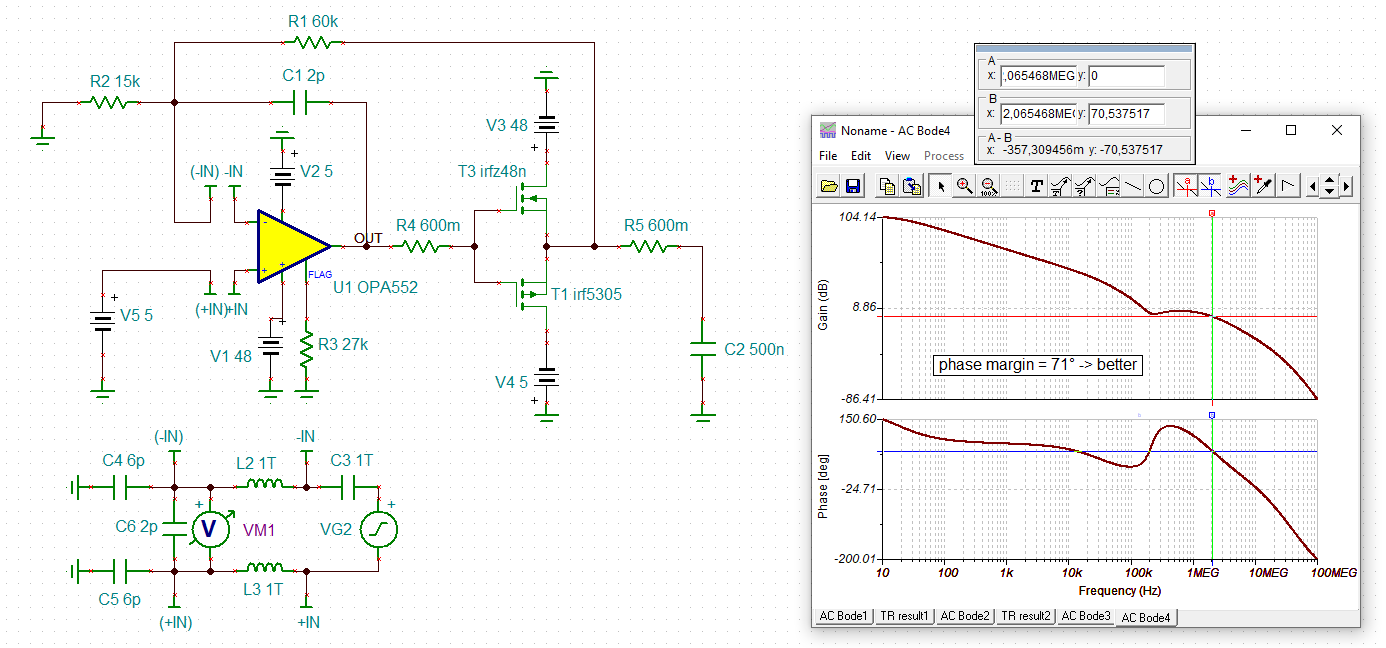

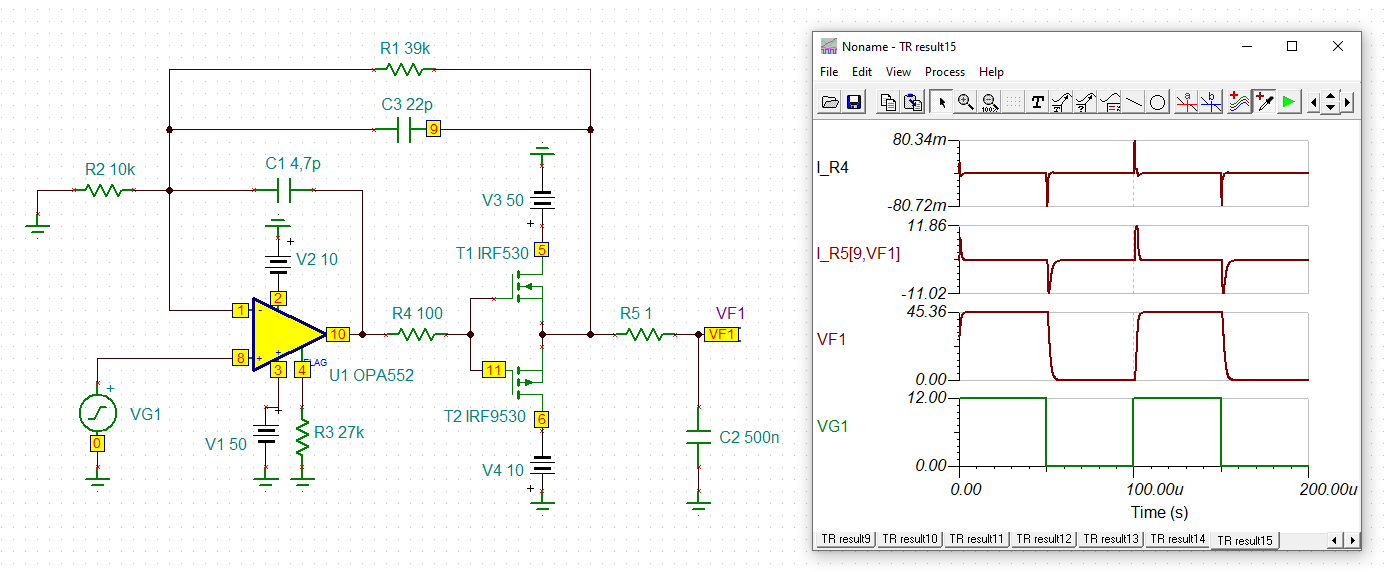

I have been trying to make some circuits to improve the slew rate for the capacitive load from 1nf until 470nf using OPA552 (DDPAK package ). Attached below is the circuit. Some insights of the circuit, the cascaded gain circuit is 5.

When the input is about 7.4volts, the device broke and until 7 volts it was alright. Vs+ = (+44V) and Vs- = (-5V) ---> A PCB was built for same circuit.

update:

Found out that the first opamp in the cascaded circuit was broken.

Please help me with this.

Please let me know if something else is required.

B.R,

Tarun