Other Parts Discussed in Thread: OPA455, OPA462, OPA452

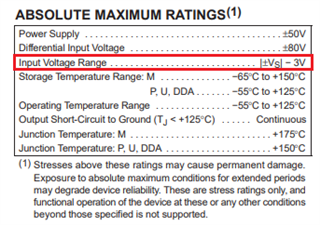

How can the OPA445 improve the slew rate of the noninverting and inverting amplifier circuits?

Currently, I am looking at the operation of the actual device, but the slew rate is several times smaller than the results of the simulation (slower)

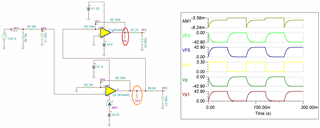

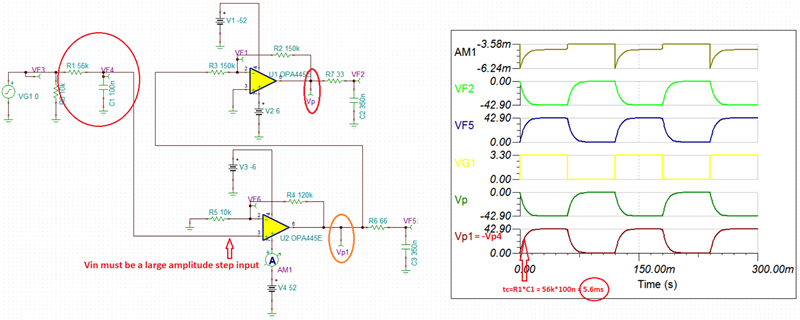

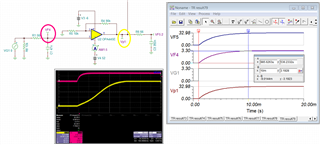

・diagram

・wave form

red: input(VF4), yellow: output(VF5)

Regards,

Hironori Kishida

Evident Corporation