During the debugging of OPA818, it was found that the bandwidth could not meet the design specifications, and it was suspected that it was the influence of parasitic capacitance, but I did not know how to eliminate it.

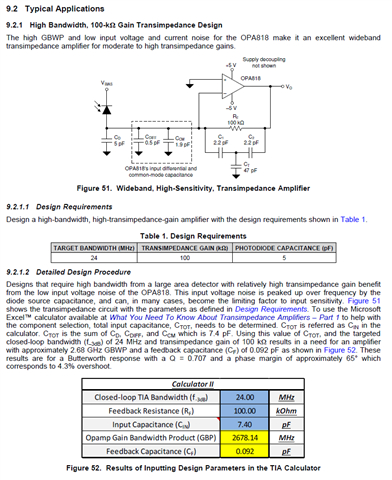

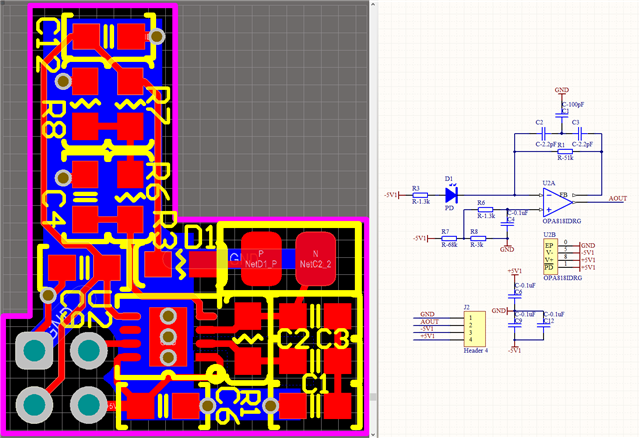

Design the circuit according to chapter 9.2 of the datasheet, the first version of PCB (thickness 1.0mm), Rf changed to 50kR, after the feedback capacitance is less than 0.3pF, change the feedback capacitor value, there is no significant impact on the bandwidth (bandwidth between 11MHz~14MHz, can not exceed 14MHz), remove the feedback capacitor network, the circuit still works normally, the bandwidth is 14MHz.

The first version of the PCB (thickness 1.0mm) changed the Rf from a single 50kR (0603 package) resistor to 20kR and 30kR resistors in series (0603 footprint), without feedback capacitors, and the bandwidth can be increased to 19MHz. However, it is still below the indicators in the manual.

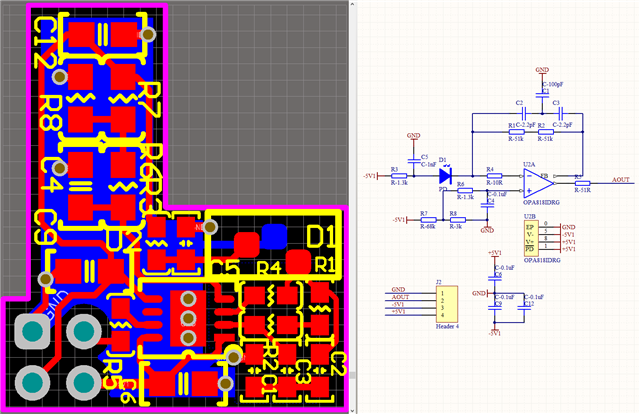

On the second version of the PCB (in order to reduce the parasitic capacitance, the board thickness was changed to 1.4mm), Rf was connected in series with 20kR and 30kR resistors (to reduce PCB area, the resistor was changed to 0402 footprint), no feedback capacitor installed, and the bandwidth was only 14MHz.

Both the chip capacitance and the photodiode capacitance have been tested, the chip capacitance is consistent with the nominal capacitance, and the junction capacitance of the photodiode is about 0.7pF under bias voltage. The bandwidth of the optical signal itself is above 50MHz.

There are the following questions:

- Why is the performance of the second version of PCB not as good as the first version?

- Does increasing PCB thickness (1.0-1.6) help reduce parasitic capacitance? Or is the impact negligible?

- Does changing the 0402 device to the 0603 device help reduce the parasitic capacitance? Or is the impact negligible?

- There is a big difference between the bandwidth calculated according to the formula and the actual measured bandwidth, is GBWP lower than the actual nominal value?

- How to reduce the parasitic capacitance?

- How to increase bandwidth without reducing transimpedance?