Part Number: LM393

,Hi,

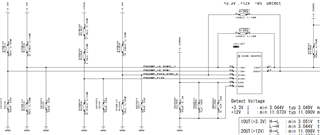

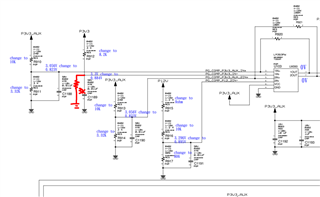

Please refer to beloe circuit.

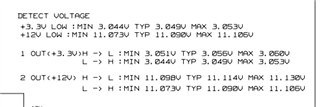

My customer design Vcc is 3.3V, so the IN+ and IN- should be lower than Vcc-2V=1.3V

The IN+ and IN- in the design is 3.3V, according below statement 4, when IN+ and IN- (3.3V) higher than common-mode (1.3V), output should be low, is that correct?