Hi team,

Here is a customer question.

Regarding D/S 7.3.5, when should the LATCH pin set to high during power-up behavior in LATCH mode?

Best Regards,

Shoji

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

Here is a customer question.

Regarding D/S 7.3.5, when should the LATCH pin set to high during power-up behavior in LATCH mode?

Best Regards,

Shoji

Hi Shoji,

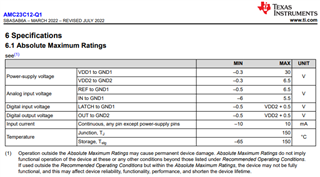

LATCH can be brought up with the VDD2 supply as long as it does not exceed VDD2 + 500mV.

Hi Alexander,

My name is Ezaka and I asked you this question.

I am considering using this product.

Thank you for your answer.

I would like to know when to enable the latch mode.

For example, after VDD1 and VDD2 are turned on, the LATCH pin is turned from Low to High, etc.

Hello Ezaka,

Happy to help!

What kind of application is this for and how is the device going to be used?

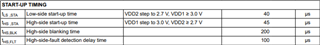

If pulling LATCH high, it can be brought up with the VDD2 supply. If pulling LATCH low, it can be kept low. Otherwise the start-up timing characteristics apply:

Hi Alexander,

We are considering using this product in an overvoltage detection circuit in a 3-phase inverter.

In this case, the latch pin is set to High because it is used in latch mode.

If the LATCH pin is set high before VDD2 (low side) rises, according to the startup operation (figure7-5), the OUT pin will go low after 140usec, but will the fault state be maintained?

Hi Ezaka,

If the LATCH pin is set high before VDD2 rises, the device may be damaged as I described in the first post.

If the device is not damaged, then I would expect the device to operate normally.

Hi Alexander,

I understood.

The absolute maximum rating of the LATCH pin is determined by VDD2, so I need to set the status after VDD2 is up.

thank you so match!