Other Parts Discussed in Thread: TLV9020

Hi,

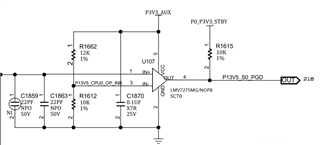

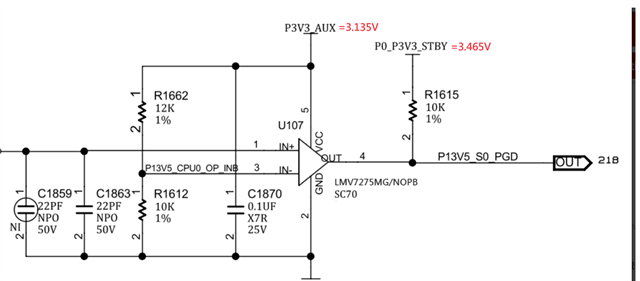

I would like to use LMV7275MG/NOPB design as below schematic, could you please help to review and provide your comment.

Do you have relative OP design and need to check portions? If you have,could you share for me?

Thanks,