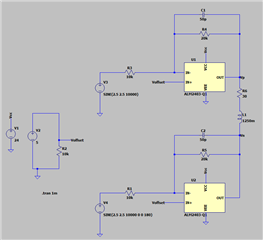

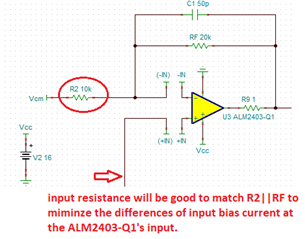

Other Parts Discussed in Thread: ALM2402F-Q1, OPA564-Q1

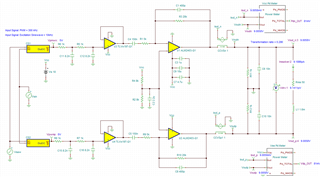

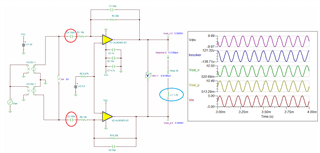

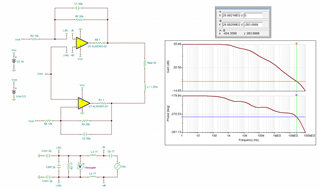

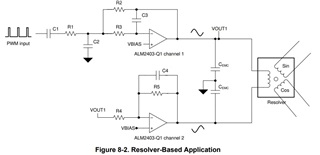

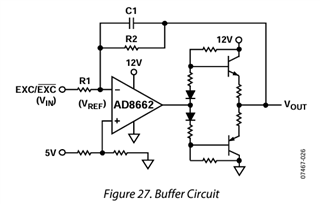

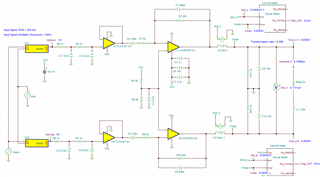

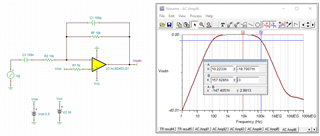

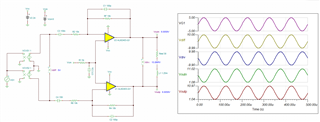

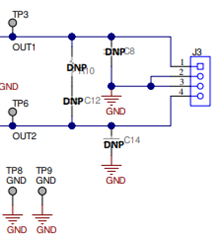

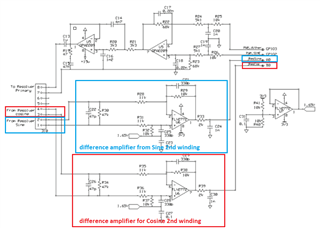

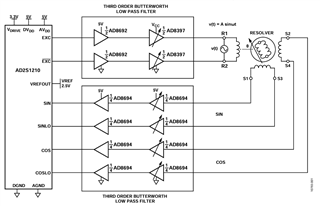

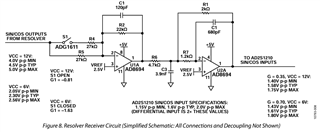

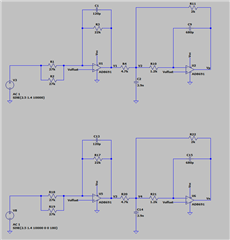

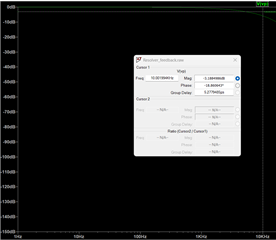

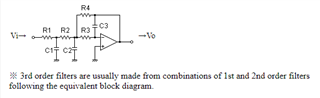

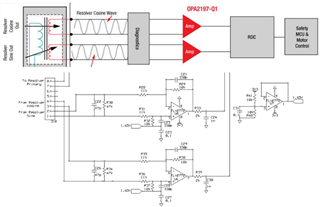

I I want to use ALM2403 to design a circuit that drives the resolver, but because the resolver is an RL load, does TI have any documents that can help me confirm how to design the circuit to avoid circuit instability?