Other Parts Discussed in Thread: INA201

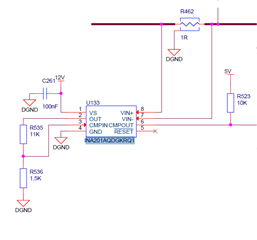

One of our designs uses INA201AQDGKRQ1 with the Vin+ and Vin- terminals connected across a 1R shunt resistor. During our built-in-test, there is no current flow across the shunt and the chip is powered by 12V.

During the build-in-test we measure the voltage of both Vin+ and Vin- terminals, with reference to GND, to assure it is isolated form other parts of the circuit.

Is there is voltage tolerance on Vin+ and Vin- that is documented during zero current flow across the shunt resistor? Or perhaps is there a leakage current value?

See snippet of circuit attached.