Tool/software:

Hello,

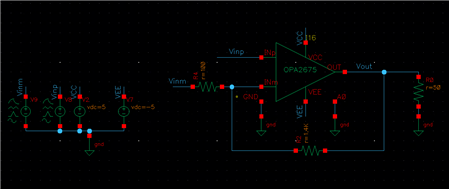

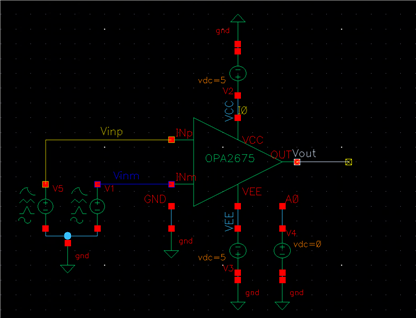

I am using the unencrypted Pspice model for the OPA2675 in a Cadence Virtuoso testbench. I am trying to drive the gates of two FETs with their own respective op amp, and I like the OPA2675 for its fast slew rate and high output current. During simulation, I noticed the slew rate of the OPA2675 is less than what I anticipate. Below is a screenshot of a separate testbench I am using to characterize the OPA2675:

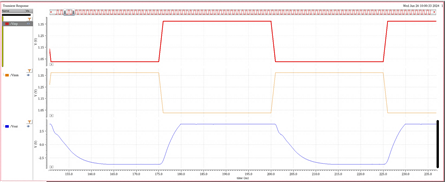

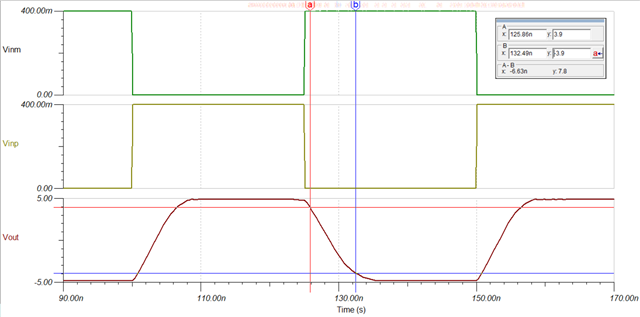

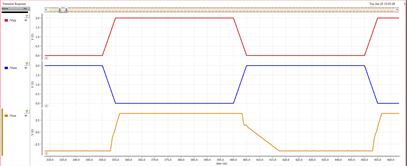

I am applying an ideal differential signal to the input terminals, and the rails are biased at ±5V. Below is a screenshot of the transient sim results for this testbench:

The rising edge of the op amp's output seems on par with the datasheet, but the falling edge is degraded. Can someone please explain why I am getting this result?

Thank you for your help!

Braden