Part Number: JFE2140

Other Parts Discussed in Thread: TINA-TI, JFE150, STRIKE

Tool/software:

Hi,

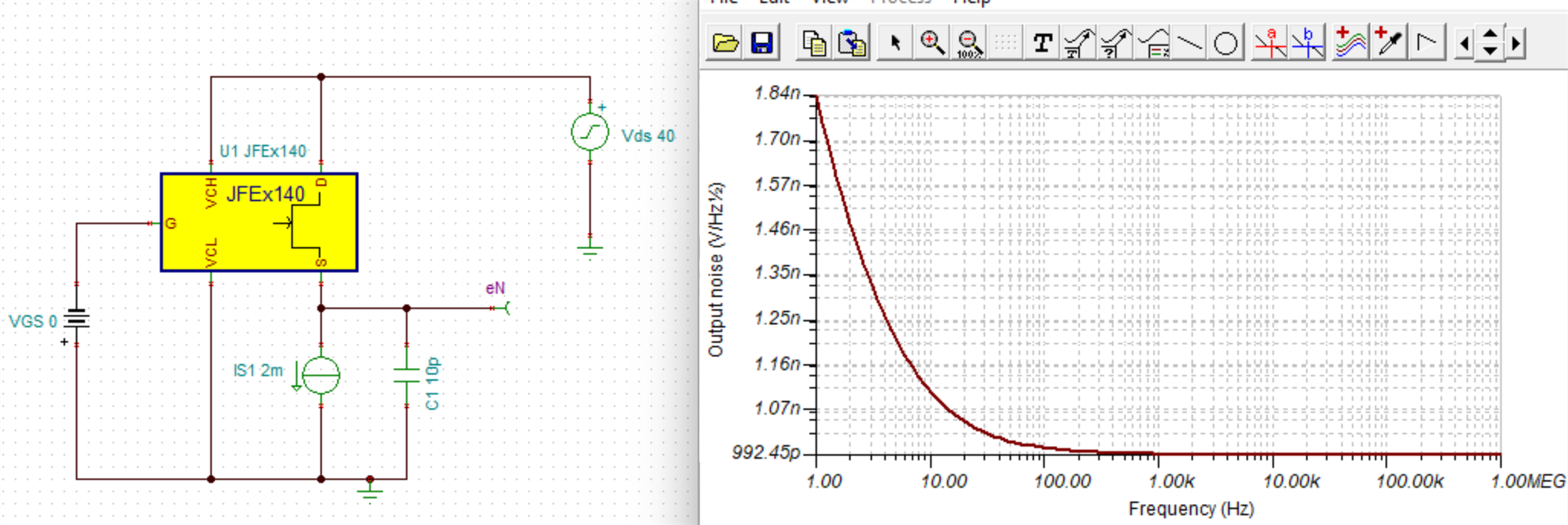

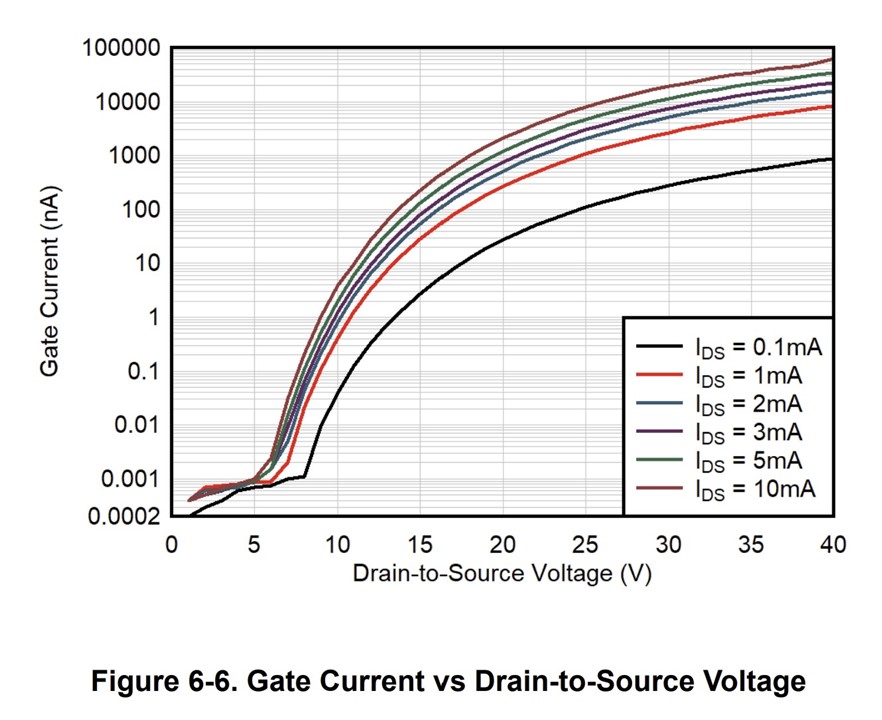

we are currently evaluating the JFE2140 and noticed a relatively big discrepancy between the Spice-Model and the real capacitances (Gate to Source and Gate to Drain) which results in a lot of additional noise in our application.

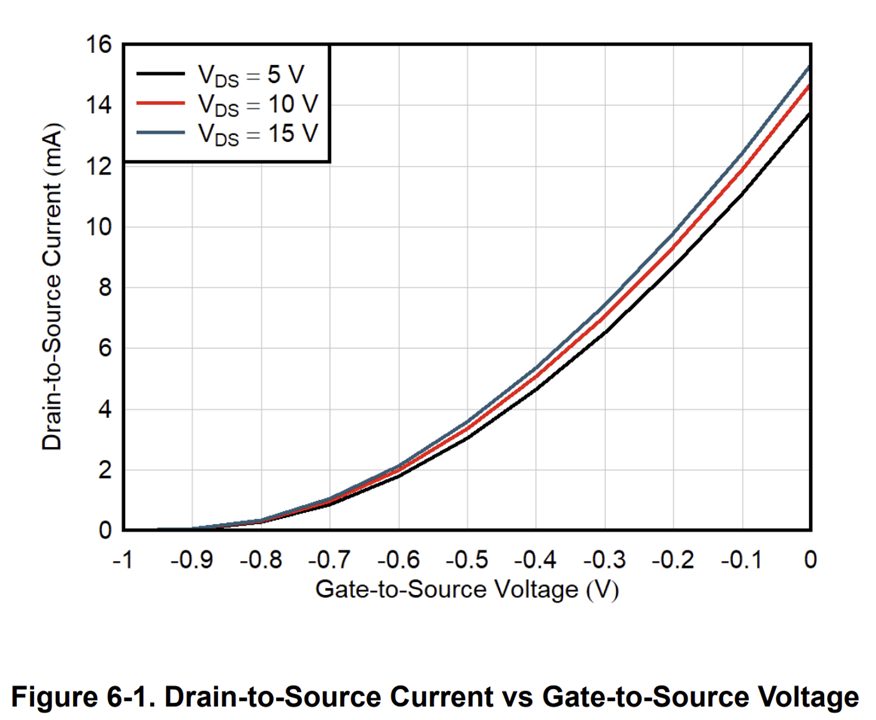

The datasheet lists some capacitances in figure 6-17 but sadly without noting at which gate voltage these measurements were taken. When measuring the capacities with an E4980A, it seems like figure 6-17 gives the capacities for roughly >0.7 V gate-source voltage.

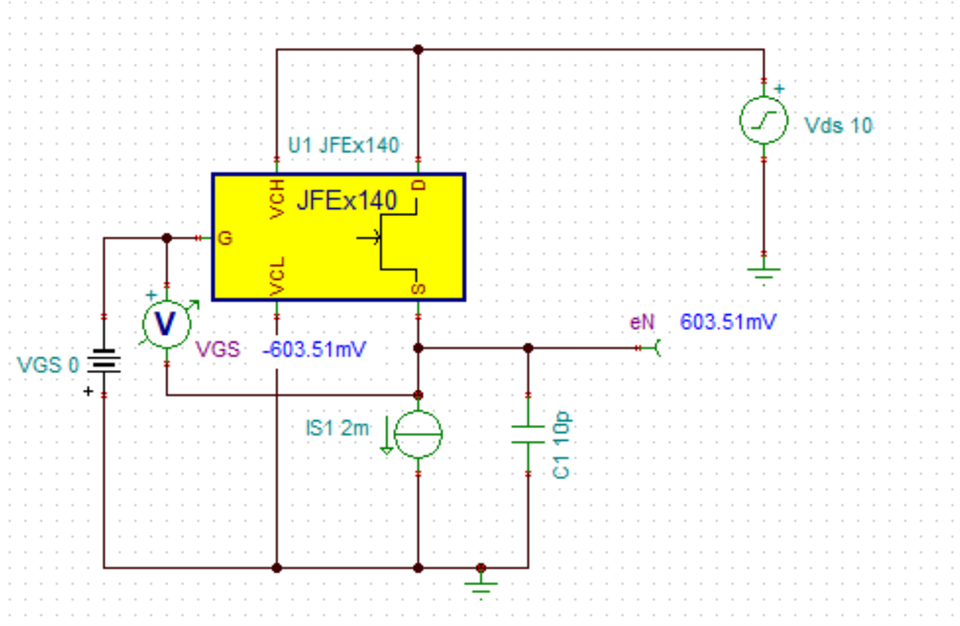

Is there more specific data available regarding the different capacities over a broader range of gate voltages? The Spice Model (using the PSpice parameters in LTspice) tells a completely different story, one which needs roughly 5 pF additional Gate-Drain and another 10 pF Gate-Source to comply with the results we are seeing in the real world.

Can someone confirm these higher capacities and the misleading behavior of the Spice models?

Best regards,

Gerrit