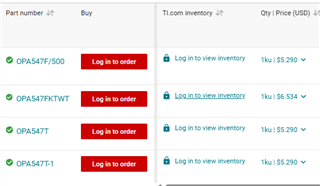

Part Number: ALM2403-Q1

Other Parts Discussed in Thread: OPA547, OPA593, OPA547EVM, OPA593EVM

Tool/software:

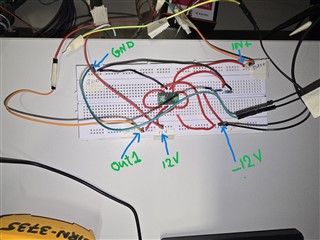

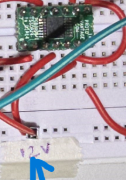

I did purchase ALM2403-Q1 dual-power op amp.

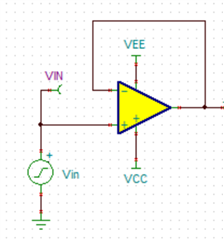

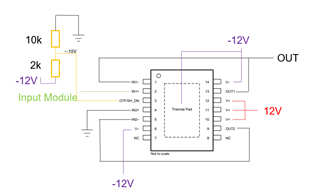

Connections made:

pin 1 : NI FPGA GND

pin2: NI FPGA Analog output ch1

pin10: +12V

pin 14: -12V

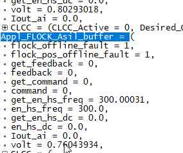

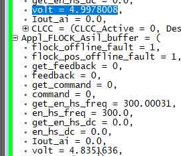

I am always getting 0V at Pin 13( OUT CH of Curr Amp CH1).

Please help identify the issue .

I have mounted the IC on 14 pin IC adaptor.