Part Number: INA597

Other Parts Discussed in Thread: MSP430FR2676

Tool/software:

Good Day,

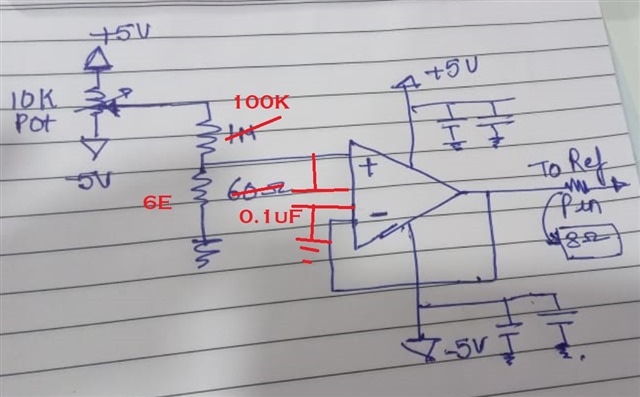

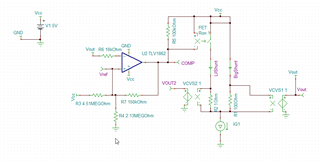

We have developed a INA597 based high side current measurement circuit. After INA597 there are 8 stages of amplifications. Because of the high gain at the last stages of amplification even the nominal offset of the INA causes saturation of the last stages.

We have tried out different offset techniques but the last attempt we are only able to zero the offset temporarily.

We could share further details in a one to one correspondence.

Looking forward to a positive response from your end.

Kind Regards,

Aditya Ayachit