Hi,

I tried to make my IFLAG high after EN is high with Vin and Vset are both 2.5V but failed.

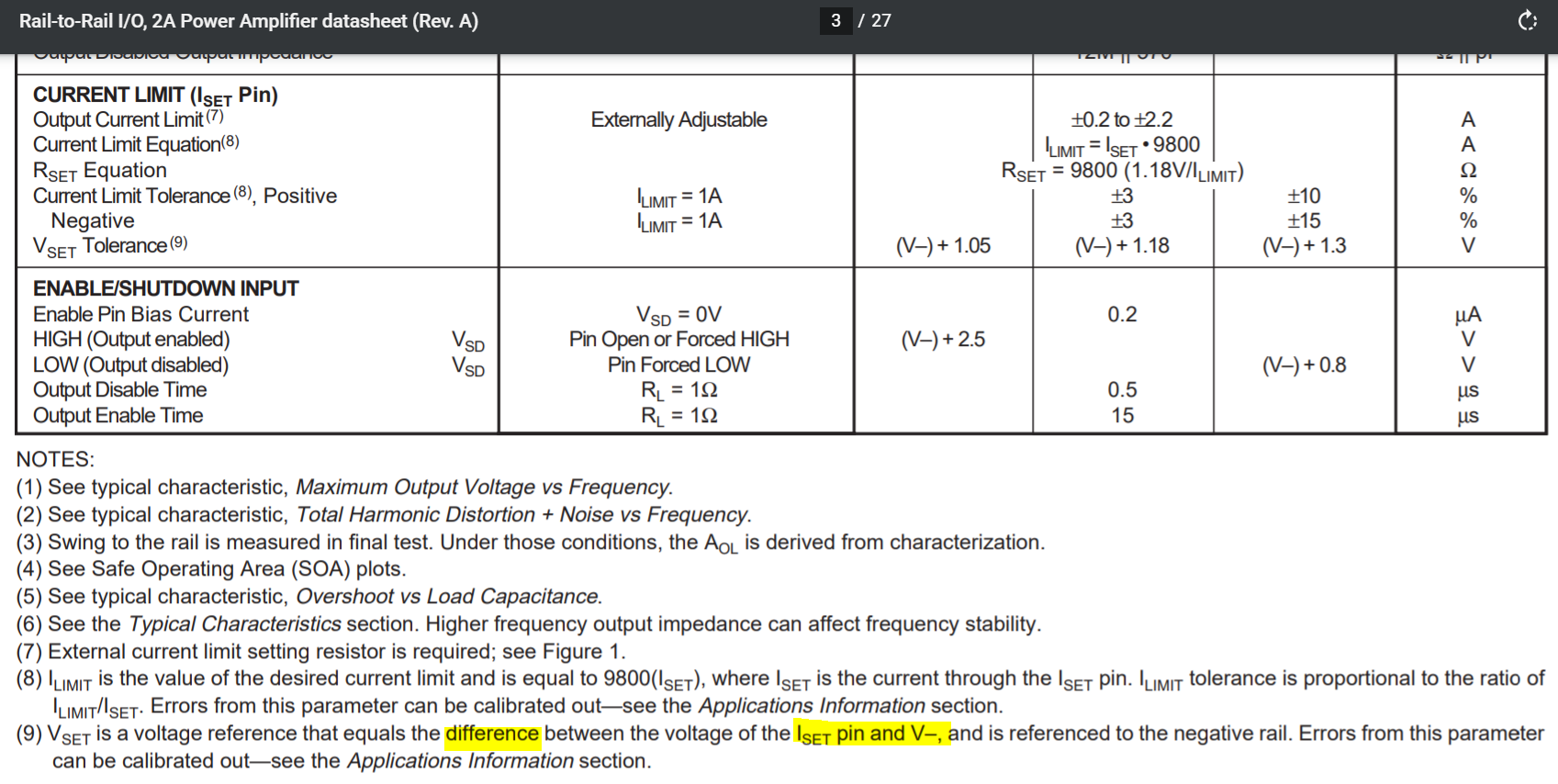

I was checking any potential cause and I found my Iset pin (pin6) is always 0V. I thought I will measure a +1.18V.

Will there really be a voltage greater than 0V on Iset pin as what described on p.3?

Thanks.