Other Parts Discussed in Thread: TMS320F28377S, , C2000WARE

Tool/software: Code Composer Studio

Hello everyone,

we are currently developing a 3-leg grid inverter. During a test, a problem has occurred where we could need some support.

The inverter runs with 70 kHz and is controlled with the Delfino TMS320F28377S.

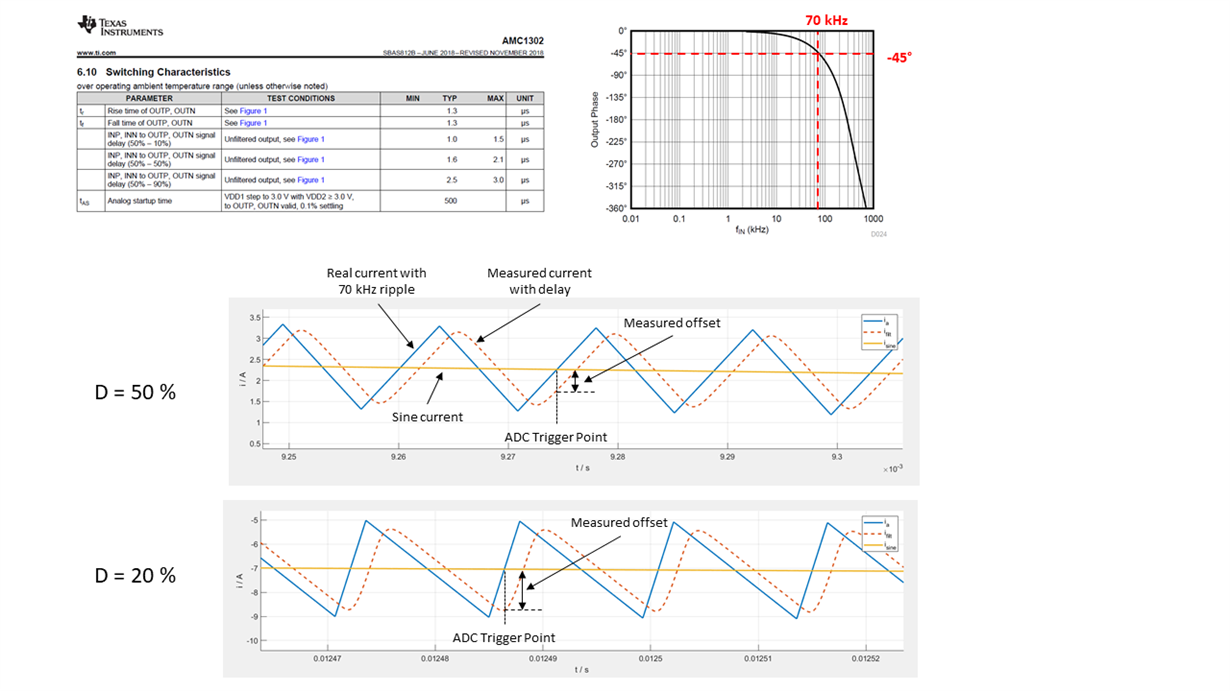

For the current sensing we are using a shunt and the AMC1302. The delay between input and output is specified here with about 1 to 3us. Looking into the phase response we got -45° phase shift at 70 kHz. This causes a not negligible error in the measured current. Our nominal current is about 10 A RMS and the ripple is about 2 A.

The error in the current measurement can reach up to 1 A, which leads us to other problems. The error is also dependent on the duty cycle.

We have already tried to compensate for the error in software, but with this big error it is not possible to make this work satisfactorily.

Here are some details from the datasheet about the delay and below I have tried to visualize the problem.

Is there a good way to compensate the error in software?

Do we need to consider another sensig IC with more bandwidth?

We are looking forward to feedback. Thank you very much in advance.

Best regards,

Simon