Dear Team,

I am using LM7171 as a clock distributor in my circuit. It is working at +15V and -15V the output from this Opamp is going to the clock input pin of my ASIC.

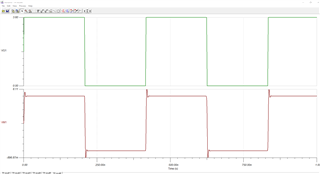

when the clock amplitude is 3.6V ,I am seeing a glitching at the output.I/P CLK frequency is 2.4Mhz

May I know where I went wrong. Please find the attached TINA simulation file.

Regards

HARI