Part Number: XTR116

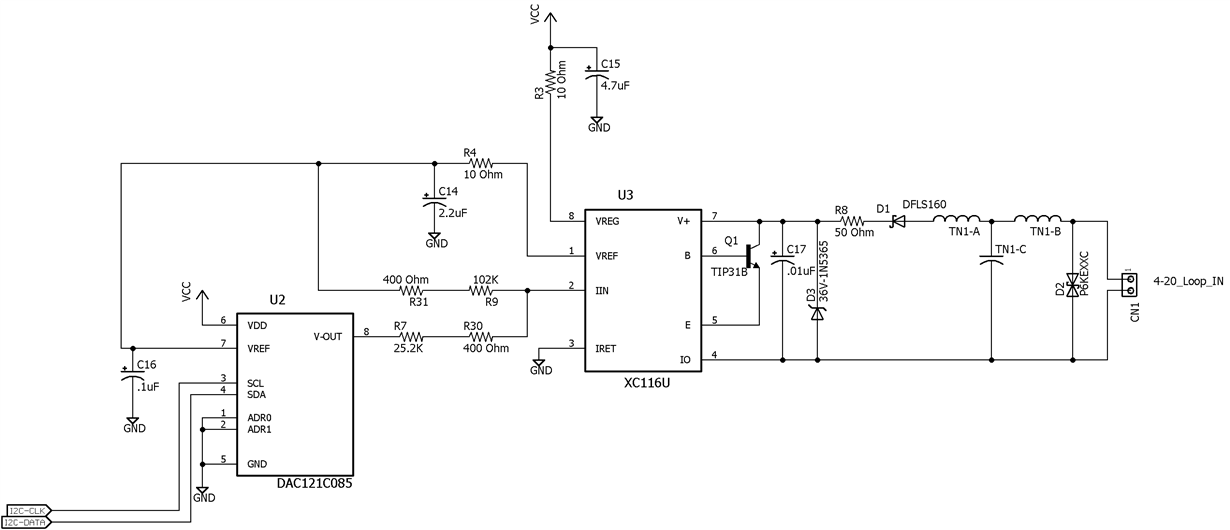

The schematic above shows what we hope is the relevant portion of our design. A few comments on the design:

1. It is a loop powered device with a PIC 18F ucontroller driving the DAC. Total current draw from the Vreg output is about 1.5 mA.

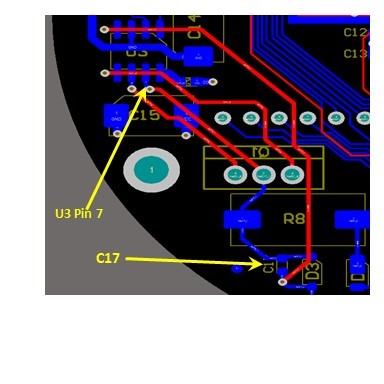

2. The Vref out of the XTR116 is connected as shown above, and goes nowhere else. The compensation for the capacitance on the line is as shown above, and there is no additional capacitance on the line, other than stray capacitance. The board layout is very tight in the area around and between the DAC and XTR116.

3. The Vreg line drives the 4.7uF cap shown on the schematic and another 1.5uF of distributed decoupling capacitors. In addition, the PIC has an internal regulator which is active in this design, and requires an external 10uF cap, which is connected to the PIC.

4. The "T" filter on the 4-20 mA input is an off-the-shelf EMI filter from TDK, part number ACH32C-333-T.

Our issue is as follows:

1. Upon applying power to the 4-20 mA loop (lab power supply set to 18 VDC with ammeter in series, but nothing else), the Vreg output goes to about 1.5 VDC and stays there. Both the Vreg and Vref outputs appear to be in current limit, with the 4-20 mA loop current going to 28 to 29 mA. This is easily repeatable, and occurs even if the PIC's reset is held active (PIC reset).

2. If the power is cycled quickly (from on to off back to on), the Vreg and Vref outputs attain their proper levels and everything functions as expected.

3. If power is turned off for a few seconds, the issue presents itself again.

Our thinking has been to increase the value of R3, but did not find much specific guidance on this during the initial design phase. We are early in our debug stage, but would appreciate any input we can get.

Thanks in advance,

Joaquin