Other Parts Discussed in Thread: TIDA-01629,

Hi,

I am using a INA240A1 in a similar configuration as the in the TIDA-01629 Reference Design: http://www.ti.com/tool/TIDA-01629

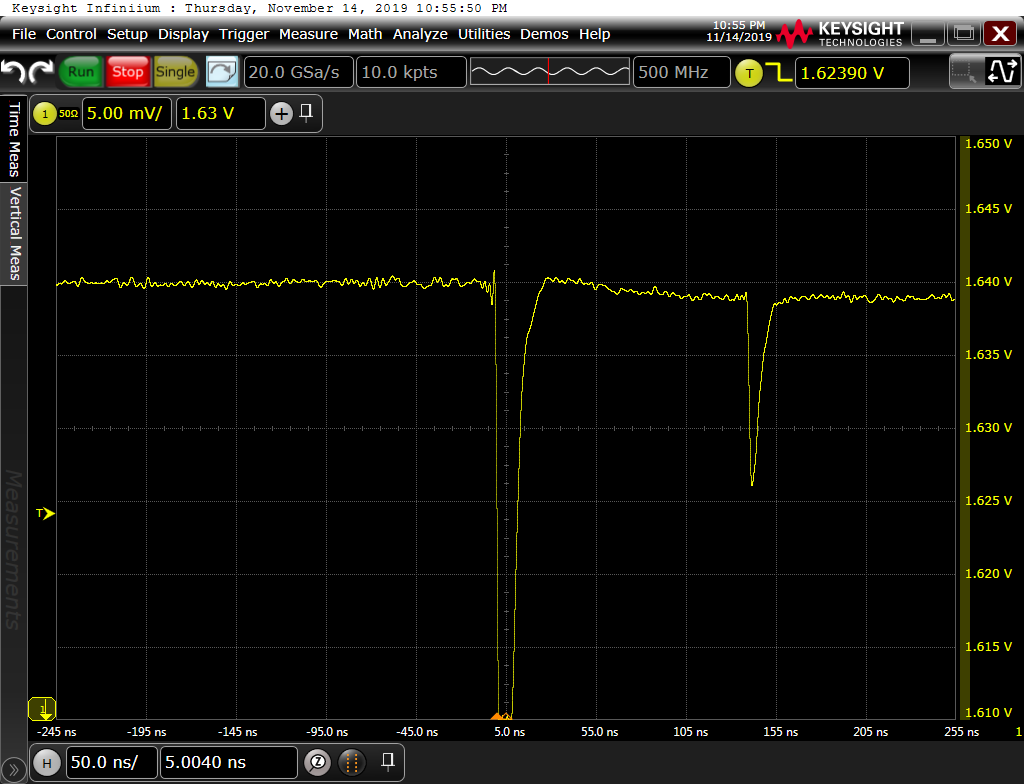

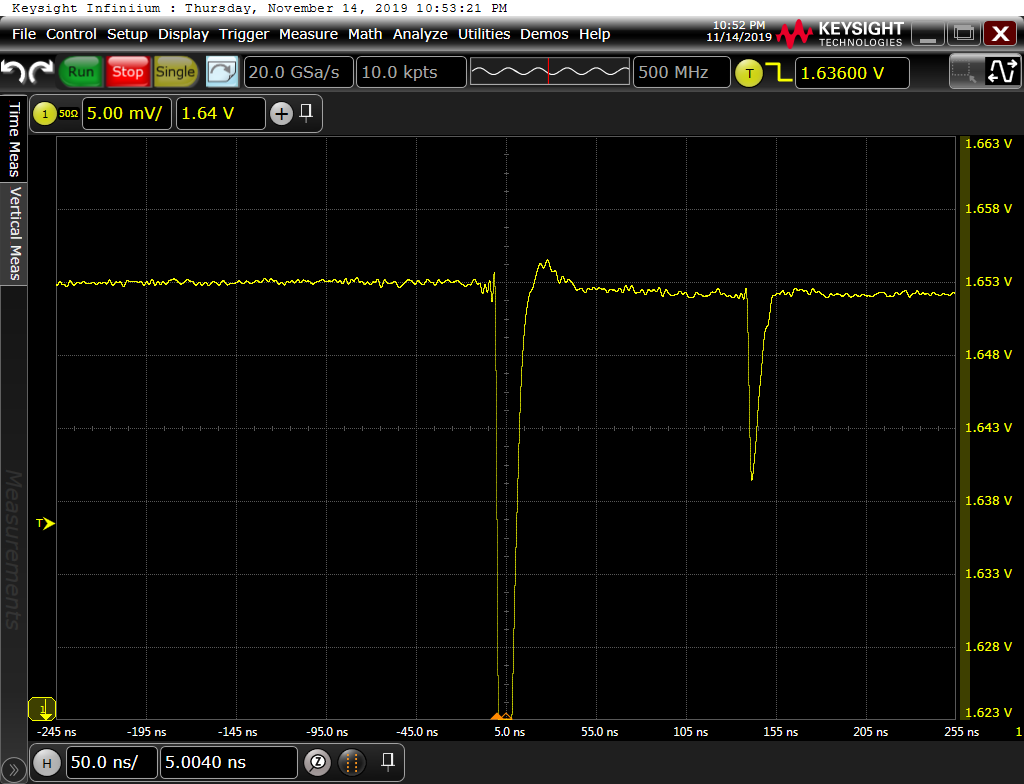

Unfortunately I see some coupling between channels sampled sequentially.

It looks like this is caused because I am using the wrong values for my RC Bucket filter between my INA240 and ADC.

In the next post: https://e2e.ti.com/support/amplifiers/f/14/p/848996/3141486#3141486

TI gives already a lot of information, but I am still not completely sure how to calculate it correctly.

I filled in the specs of my MCUs ADC (STM32F3) in the Analog Engineer's Calculator:

How do I calculate the Gain Bandwidth of the INA240A1? Is this 20*400kHz = 8MHz? So do I need to increase my sampling time to >450nS

How should I handle the Zout of the INA240 plotted in the previous topic?

How do I verify that the INA240A1 is stable with the calculated values.

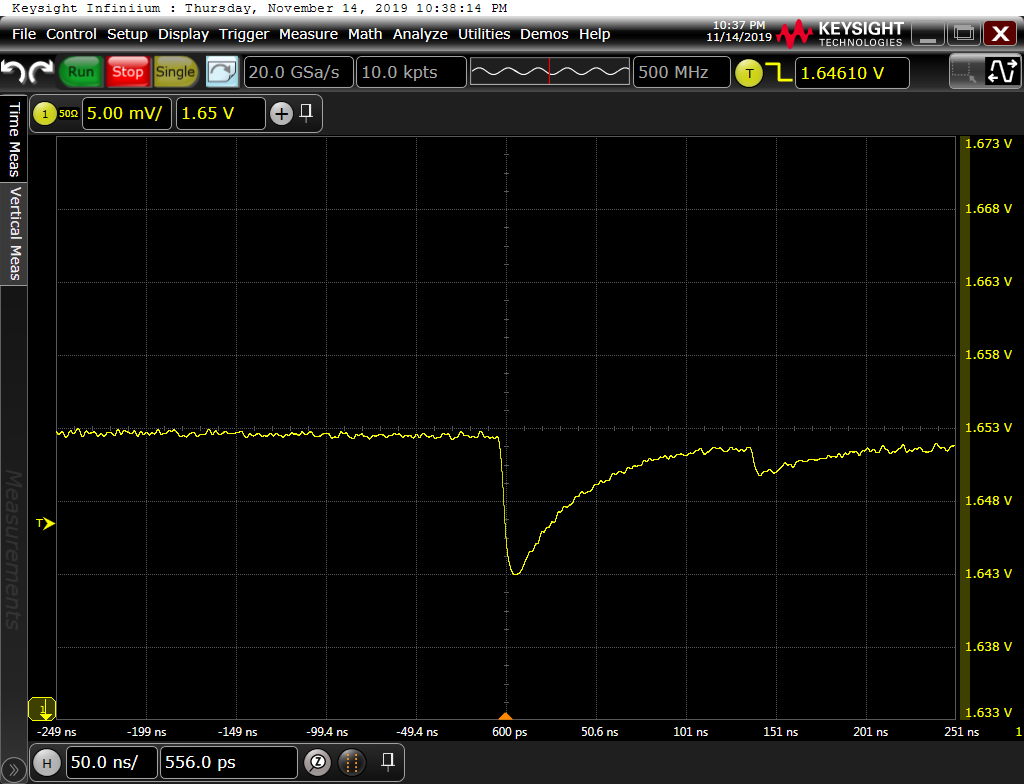

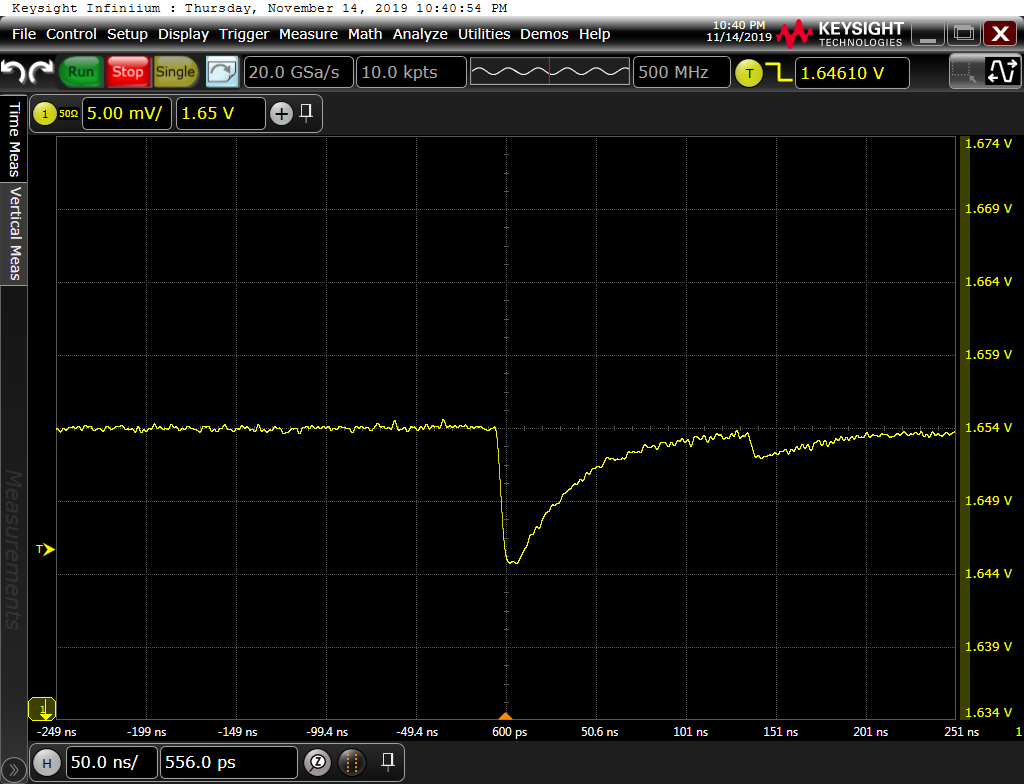

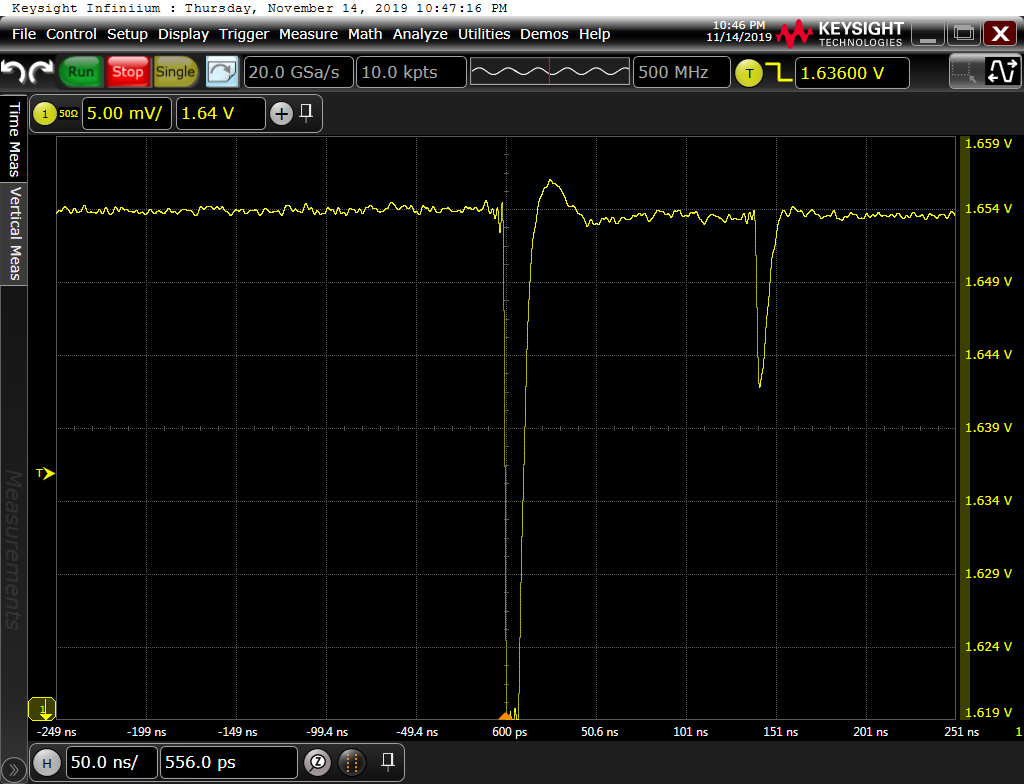

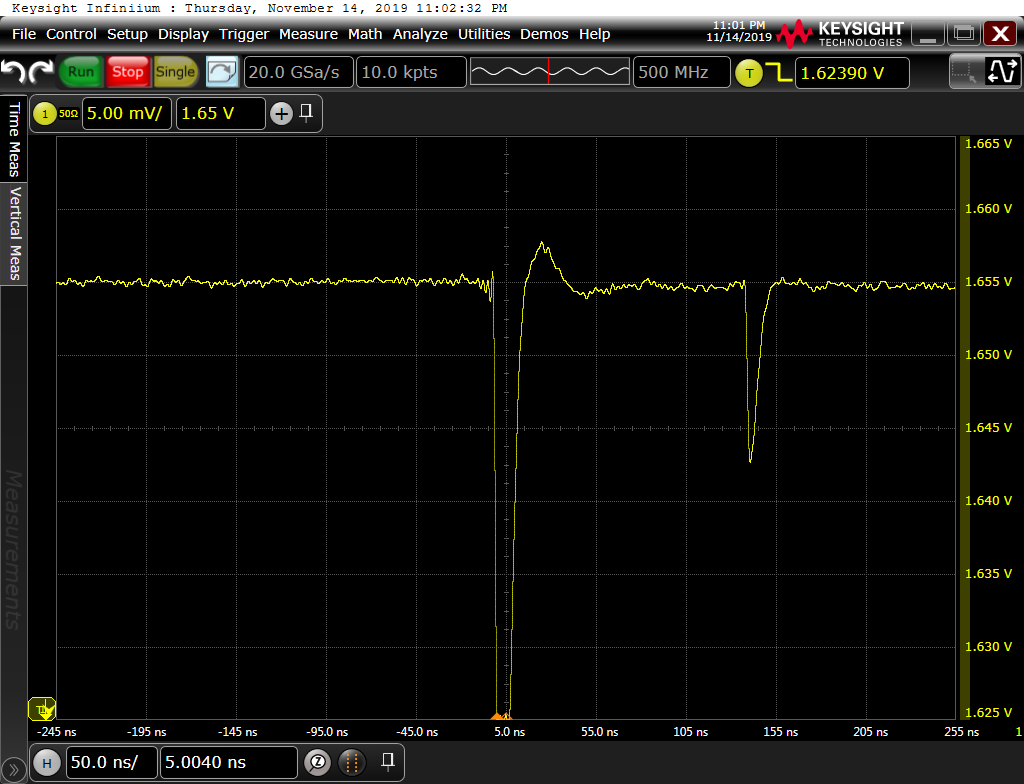

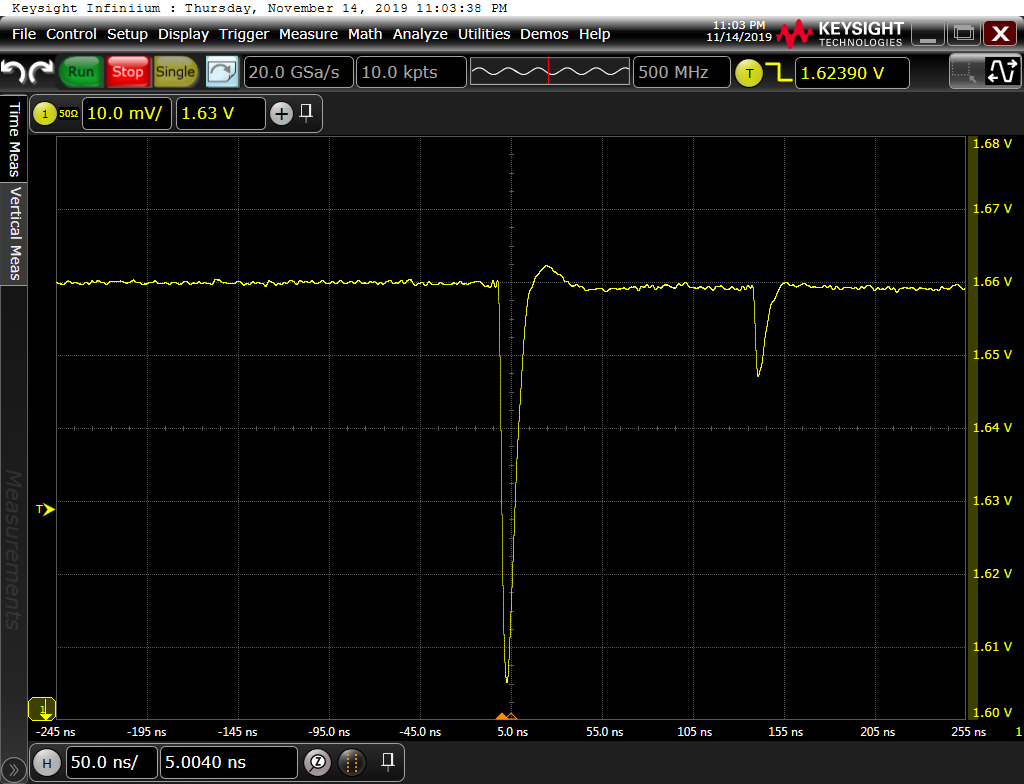

Is it also a good approach to measure with a Keysight N7020A Probe over the Capacitor (100pF) and adjust the resistance values till I have a critical damped response when the Sampling Capacitor is switched on?