- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

My customer have the DIR9001 to receive a SPDIF signal and transmit that data to the DIT4096 via I2S. Then the DIT4096 outputs the SPDIF signal to some external receiver.

What is the best way to connect/setup the CLK setting on the DIT4096 in hardware mode?

From the DIT4096 datasheet:

Thanks,

Connie

Hello Connie,

Thanks for your patience I will need to review both datasheets and find optimum configuration for you based on what you detailed. I will reply back within 48 hours.

Best Regards,

Low Power Audio Engineer

Hello Carson,

My name is Austin and I am the customer working with Connie on this part.

I believe the sample date rate is variable as the multiple different sources could have different data rates.

Hello Austin,

Would those varying sample rates abide by at least one of the three master clock ratios seen in that lower figure?

And what is the MCLK frequency you plan to use?

Carson

Hello Carson,

Yes, the varying Sample Rates would abide by the master clock ratios.

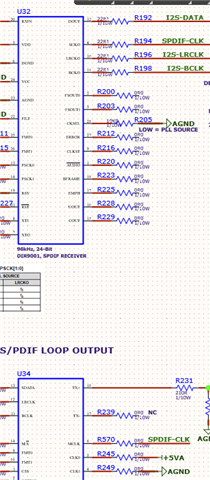

The MCLK would come from the DIR9001 SCKO output. Schematic snippet below:

Hello,

By what you have described you would need to just have something controlling the input lines of CLK0 and CLK1 to change setting accordingly with the changing sample rate.

Carson