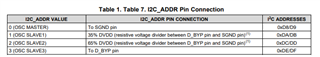

# Issue: I can't R/W the SLAVE AMP (only used salve2). But MASTER R/W reg. are OK (except reg. 0x0A can't set to 0x40).

# My initial sequence:

- Read from master register 0x00 => value = 0x00

- Read from master register 0x01 => value = 0x00

- Write to master in the register 0x0A 0x40

- Read from master register 0x0A => value = 0x00 <== can't write

- Write to master in the register 0x0B 0xC0

- Read from master register 0x0B => value = 0xC0

- Read from slave register 0x00 => value = 0xdd <== get wrong value

- Read from slave register 0x01 => value = 0xdd <== get wrong value

- Write to slave in the register 0x0B 0x10

- Read from slave register 0x0B => value = 0xdd <== get wrong value

- Write to master in the register 0x0C 0x10 <= set to mute mode

- Read from master register 0x0C => value = 0x10

- Read from master register 0x06 => value = 0x0F <== ???

- Write to master in the register 0x0C 0x00 <= set to play mode

- Read from master register 0x0C => value = 0x00

- Read from master register 0x06 => value = 0x0F

- OSC_SYNC pin => 4MHz <== ???

# that's right?

Thank you.