Other Parts Discussed in Thread: TIDA-01410

Hi,

on my (selfmade) testboard for the LMX2594 I measured a big difference in spurious for integer vs. non-integer mode:

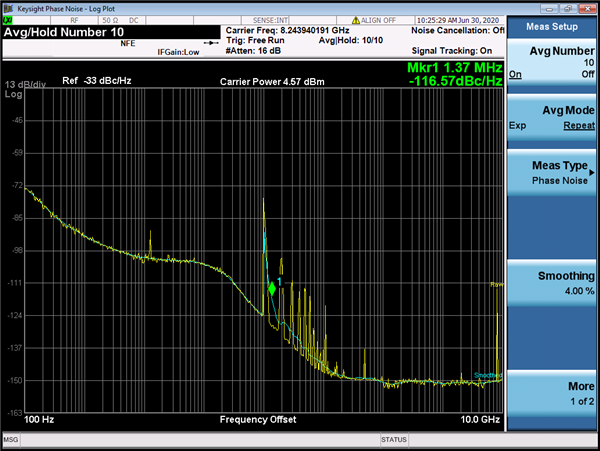

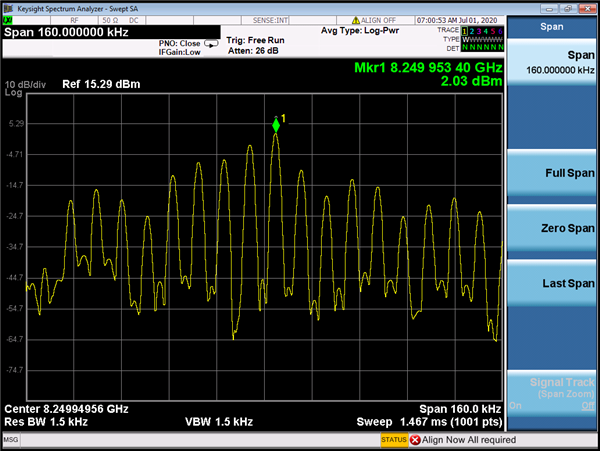

Non-integer mode:

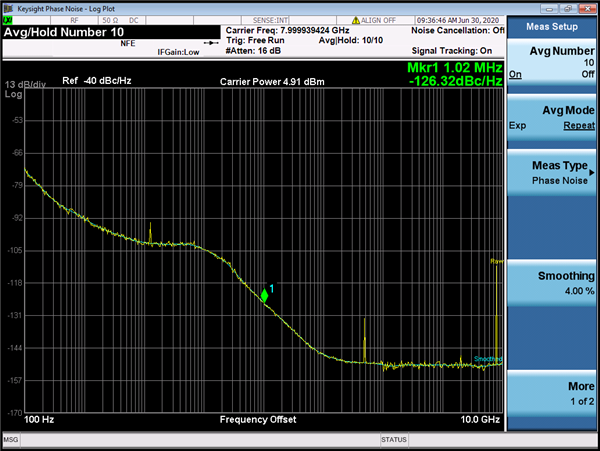

Integer mode:

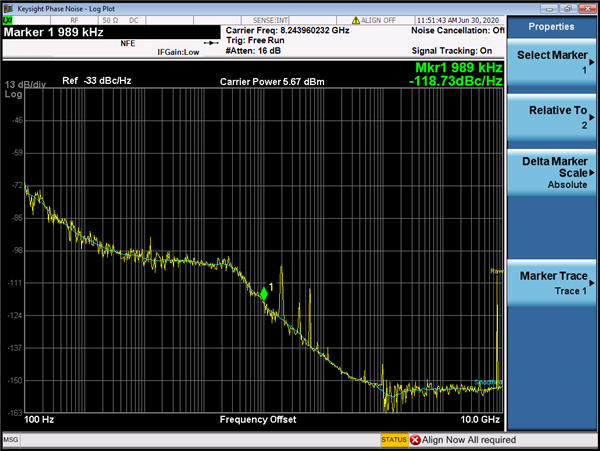

Here you can finde the settings in TICS Pro (non-integer mode):

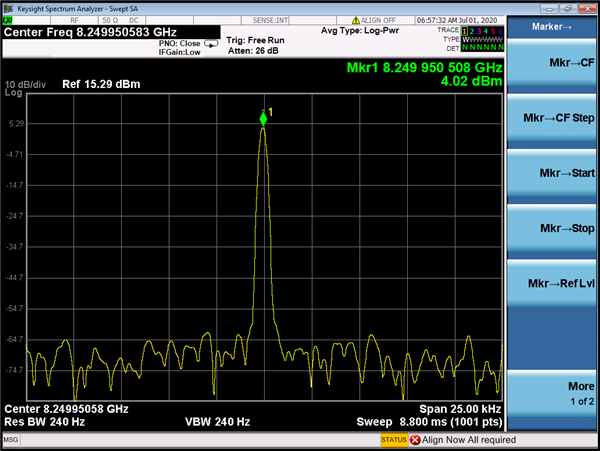

The goal is to produce an output frequency of 8.244 GHz. How can we reduce the spurious for this frequency?

Thank you very much in advance.

Best regards

Joachim