Other Parts Discussed in Thread: LMK04832, LMK00301

Hey

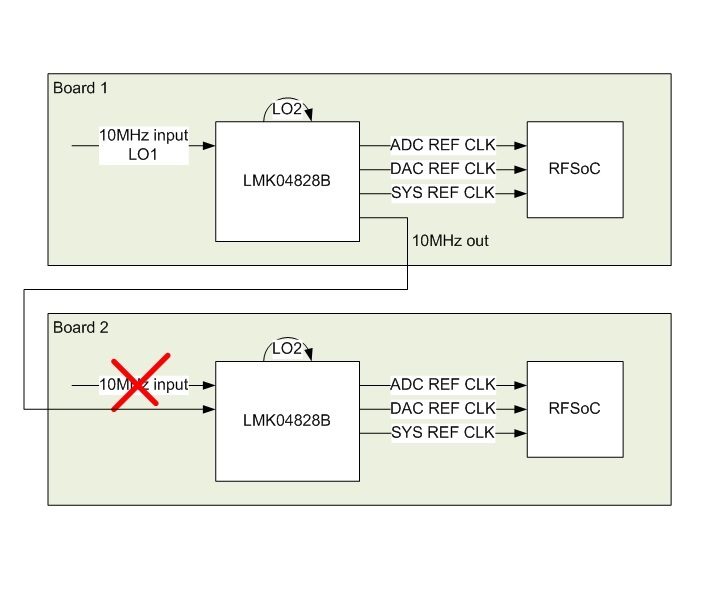

I have a system that contains several boards with High Speed ADCs and DACs (base on Xilinx RFSoC), for each one of the boards the clock input to the ADCs and DACs reference clock is generated by LMK04828 device.

Since the LMK04828 device required dual - input crystal and local oscillator

I wanted to ask if there is a way the I can synchronize between my boards DAC/ADC reference clock using multiple LMK0482B’s

Please see illustration

My concern is LO2 that is different between the two boards

is there a way to do that?

BR