Hi,

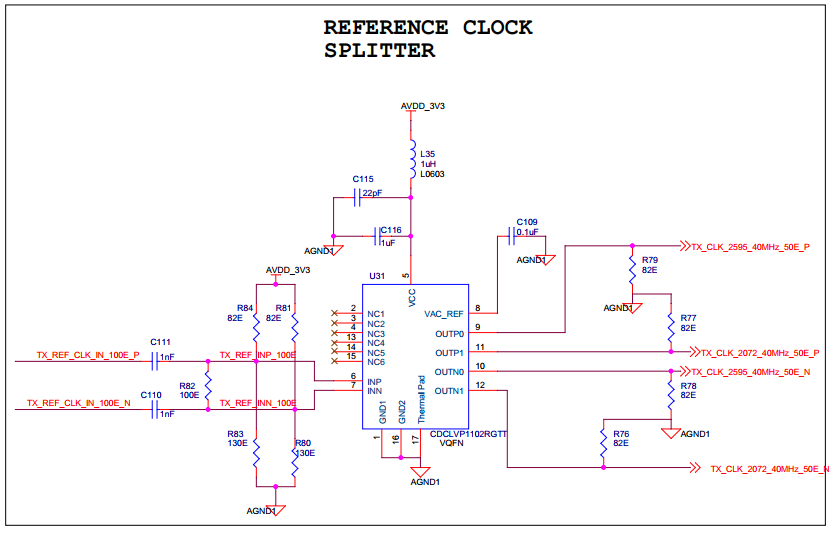

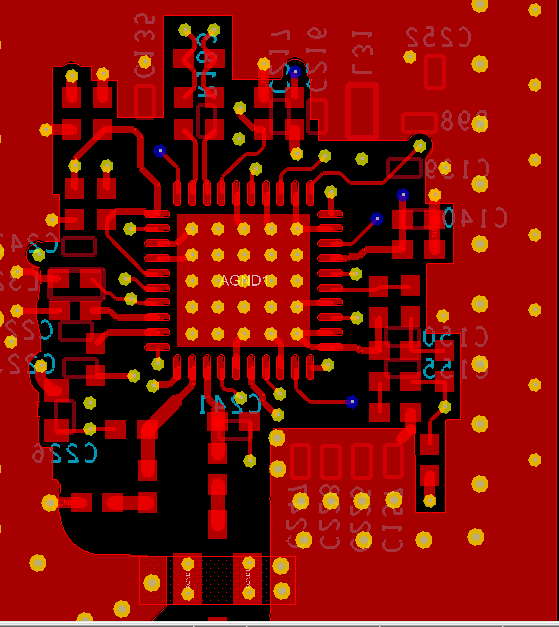

I have observed 30dB degradation in phase noise in our board compared to EVM output.

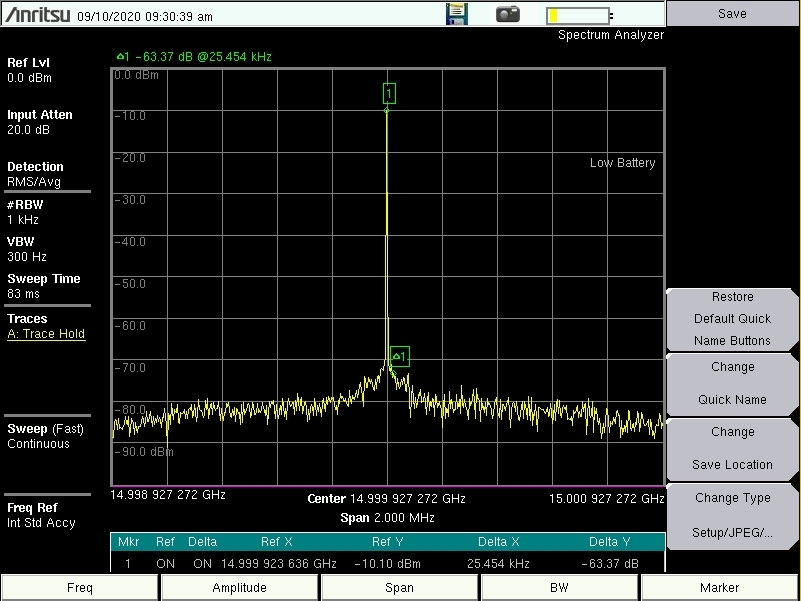

Below is the EVM output

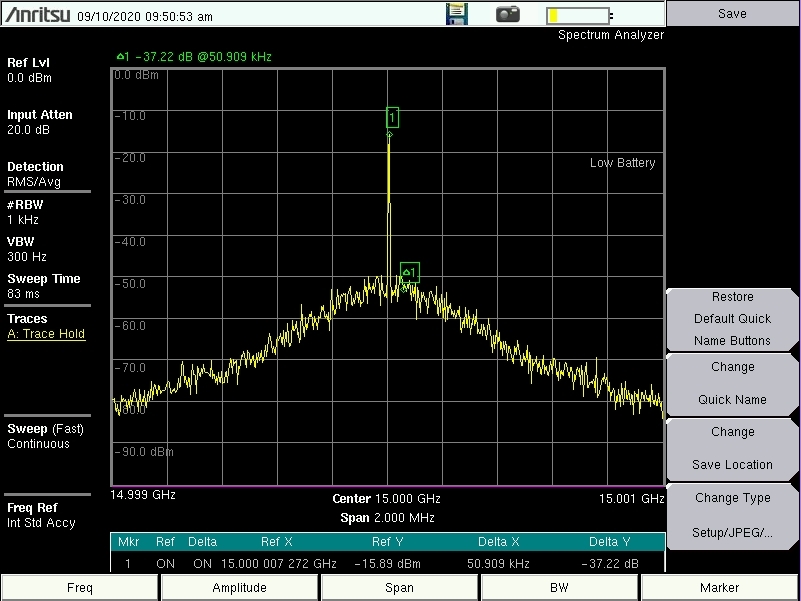

And below is the output from our board(probed:so amplitude may not be actual)

What could be the reason for such high noise around the carrier? Reference clock is clean having more that 70 dBc delta for the same setting.

T

T