Hello team,

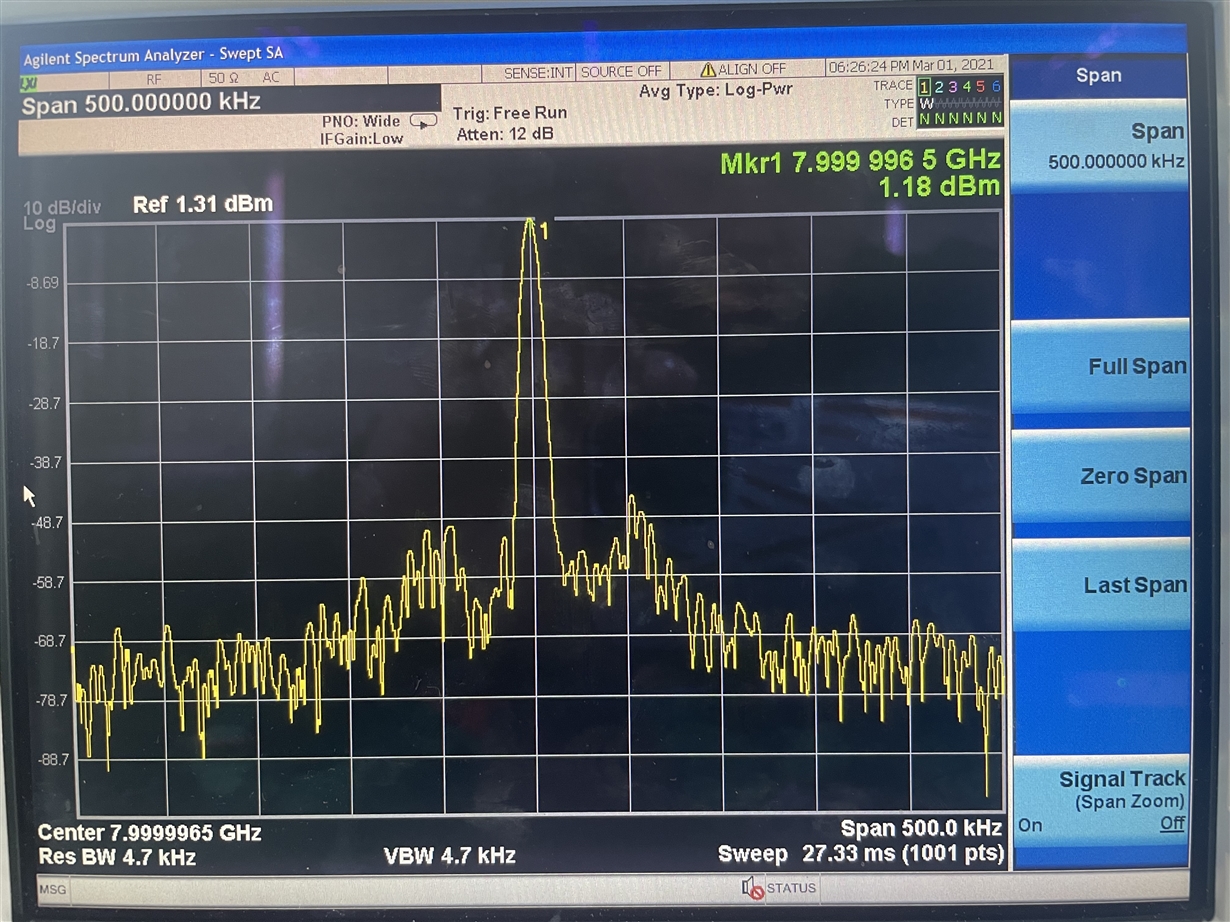

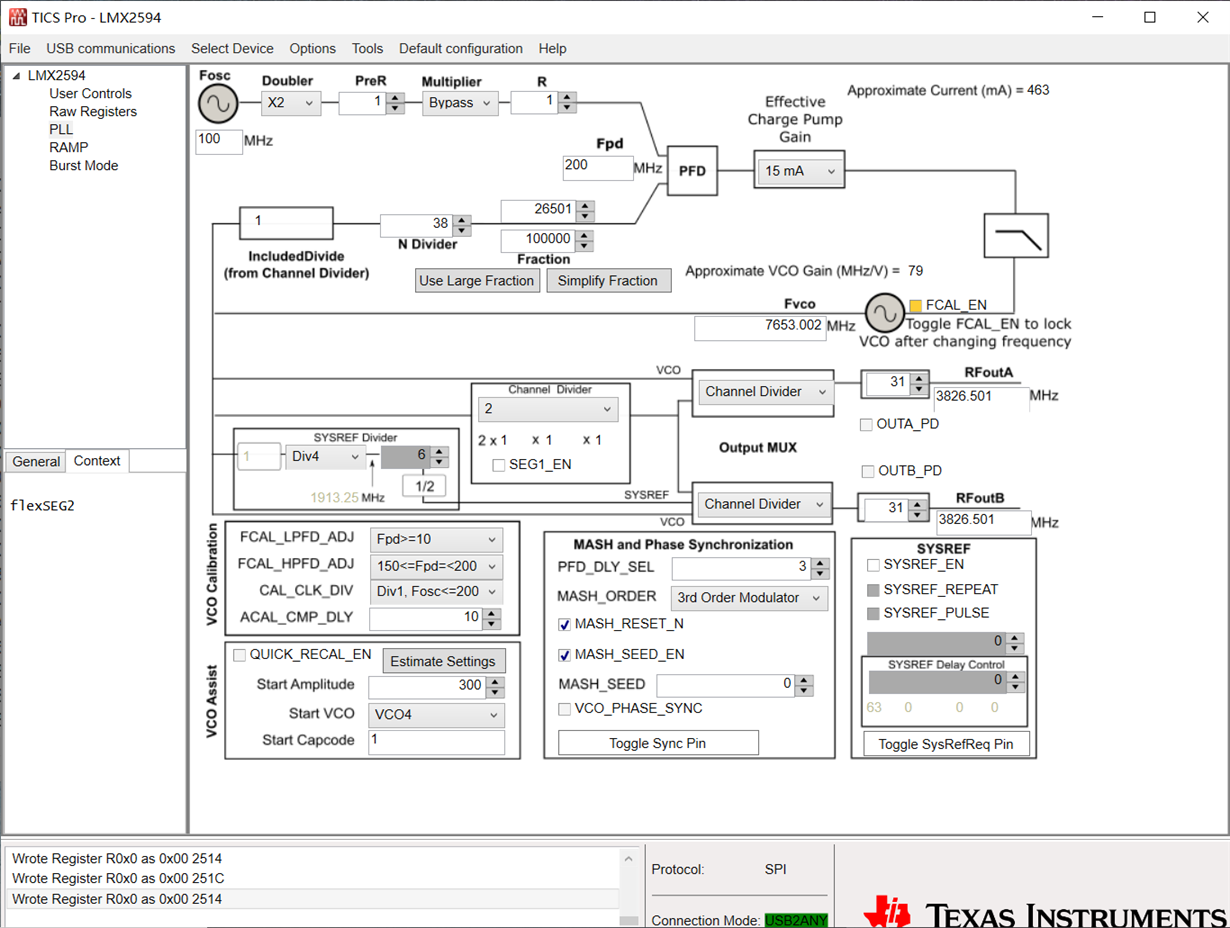

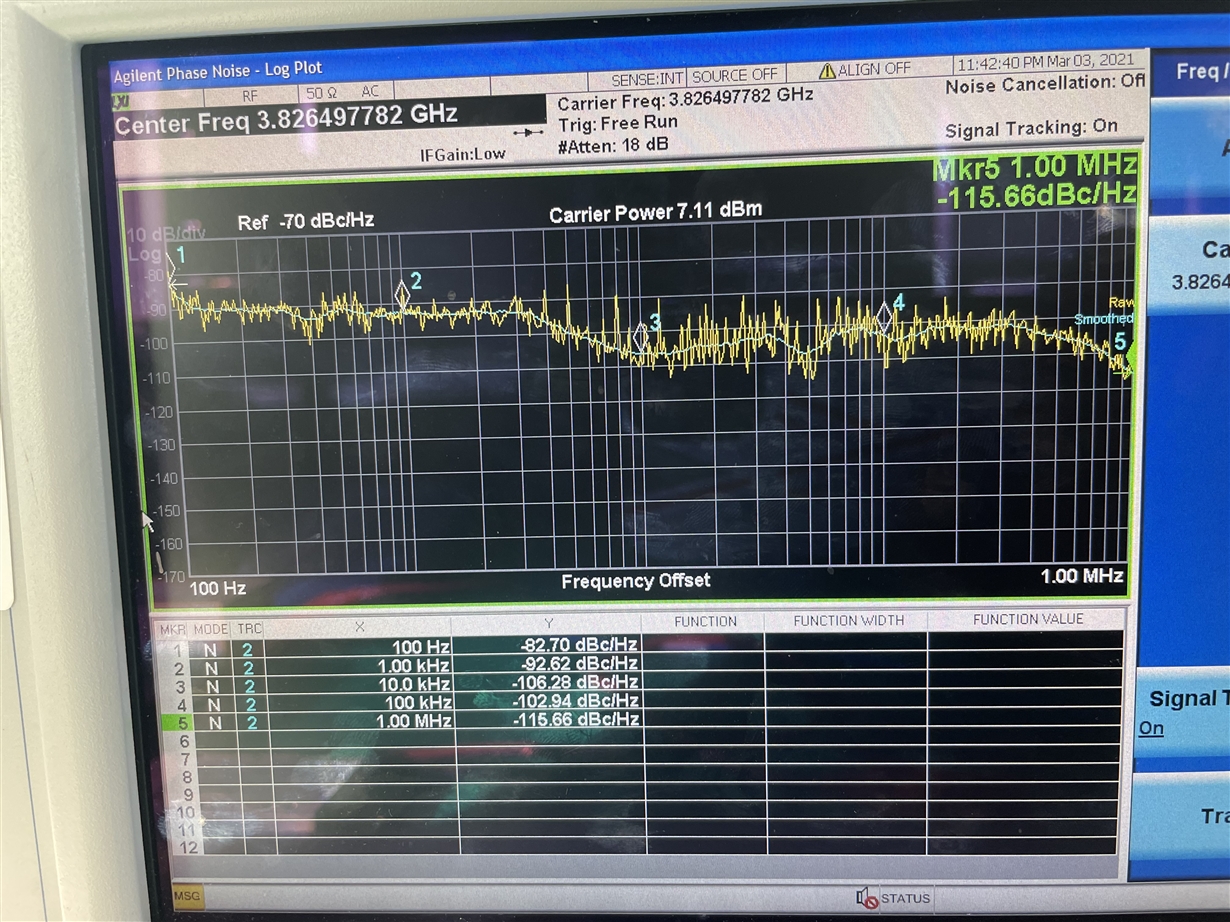

I'm building up a personal project of LO using LMX2594. The register configuration is as below. The PCB schematic is referencing the LMX2594EVA including the loop filter setup. But I'm getting an undesirable phase noise around 60k across the whole output frequency band. I'm not sure which part of the design goes wrong, please help! The output RF spectrum and phase noise at 8GHz is attached below. I can provide more details if needed.