- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dear Clock team,

I was advised to contact you again from Data Converters team as the following,

DAC34H84EVM: J10/J11 CDCE62005 LVDS clock output error.

Please review attached configuration files from the customer.

- DAC_config_CDC.txt : Configuration file for CDCE62005 device only

- DAC_config_full.txt : Configuration file including DAC34H84 device

They found a issue. When they set the DAC register "x02", DAC32H84 device settings became default value, although CDCE62005 device settings was kept as the configuration file.

When they read the register value after loading "DAC_config_full.txt", it became different value as the following,

- DAC_config_full_Read_after_Load.txt

x00 x0000 x01 x0000 x02 x0000 x03 x0000 x04 xE5B1 x05 x3A60 x06 x3100 x07 x0000 x08 x0000 x09 x0000 x0A x0000 x0B x0000 x0C x0000 x0D x0000 x0E x0000 x0F x0000 x10 x0000 x11 x0000 x12 x0000 x13 x0000 x14 x0000 x15 x0000 x16 x0000 x17 x0000 x18 x0007 x19 x0000 x1A x0020 x1B x0000 x1C x0000 x1D x0000 x1E x0000 x1F x0000 x20 x0000 x22 x0000 x23 x0000 x24 x0000 x25 x0000 x26 x0000 x27 x0000 x28 x0000 x29 x0000 x2A x0000 x2B x0000 x2C x0000 x2D x0000 x2E x0000 x2F x0000 x30 x0000 x7F x0001 CDCE62005 Registers Freq:19.200000MHz Address Data 00 00400000 01 81860301 02 81860302 03 C1860303 04 C1860304 05 28001A95 06 44AF24F6 07 145294A7 08 20001808

x00 x019F x01 x0402 x02 x7082 x03 xA000 x04 x0000 x05 x0000 x06 x0000 x07 xD8FF x08 x0000 x09 x8000 x0A x0000 x0B x0000 x0C x0000 x0D x0000 x0E x0000 x0F x0000 x10 x0000 x11 x0000 x12 x0000 x13 x0000 x14 x0000 x15 x0000 x16 x0000 x17 x0000 x18 x2460 x19 x1034 x1A x1800 x1B x0800 x1C x0000 x1D x0000 x1E x1111 x1F x1140 x20 x1101 x22 x1B1B x23 xFFFF x24 x0000 x25 x0000 x26 x0000 x27 x0000 x28 x0000 x29 x0000 x2A x0000 x2B x0000 x2C x0000 x2D x0004 x2E x0000 x2F x0000 x30 x0000 x7F x0001 CDCE62005 Registers Freq:19.200000MHz Address Data 00 00400000 01 81860301 02 81860302 03 C1860303 04 C1860304 05 28001A95 06 44AF24F6 07 145294A7 08 20001808

x00 x0000 x01 x0000 x02 x0000 x03 x0000 x04 xFFFF x05 x267E x06 x3300 x07 x0000 x08 x0000 x09 x0000 x0A x0000 x0B x0000 x0C x0000 x0D x0000 x0E x0000 x0F x0000 x10 x0000 x11 x0000 x12 x0000 x13 x0000 x14 x0000 x15 x0000 x16 x0000 x17 x0000 x18 x0007 x19 x0000 x1A x0020 x1B x0000 x1C x0000 x1D x0000 x1E x0000 x1F x0000 x20 x0000 x22 x0000 x23 x0000 x24 x0000 x25 x0000 x26 x0000 x27 x0000 x28 x0000 x29 x0000 x2A x0000 x2B x0000 x2C x0000 x2D x0000 x2E x0000 x2F x0000 x30 x0000 x7F x0001 CDCE62005 Registers Freq:19.200000MHz Address Data 00 00400000 01 81860301 02 81860302 03 C1860303 04 C1860304 05 28001A95 06 44AF24F6 07 145294A7 08 20001808

I look forward to your reply.

Thank you.

Best Regards,

Koshi Ninomiya

Hi Koshi,

This is a DAC's GUI and I am not familiar of that, how the clocking device is programming. But, I can provide my guidance to some extent.

As generated frequency (211.29MHz) is different than the programming (207.36MHz), that means CDCM device is not locked and on-board LED is OFF. Please confirm?

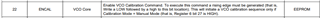

You can try to calibrate the VCO by toggling R6[22] ("1" -> "0" -> "1") while R6[27] = "0", then you should see the PLL locked and can generate correct frequency.

Regards,

Ajeet Pal

Hi Ajeet-san,

The customer tried to toggle Register 6 between the followings, but on-board LED was still OFF.

<Register 6>

40AF24F6 [1000"0"0010"1"011110010010011110110]

408F24F6 [1000"0"0010"0"011110010010011110110]

Best Regards,

Koshi Ninomiya

Hi Koshi-san,

Oh! so there is a confusion regarding the bit 22. It's for the register 6 and if they considering register address also, then it would be 26th bit.

It will be ,

<Register 6>

44AF24F6 [01000"1"00101011110010010011110110]

40AF24F6 [01000"0"00101011110010010011110110]

44AF24F6 [01000"1"00101011110010010011110110]

Please try this and see the performance.

Regards,

Ajeet Pal

Hi Ajeet-san,

The customer tried the followings, but it was not improved and on-board LED was still OFF.

#1:

44AF24F6 [01000"1"00101011110010010011110110]

40AF24F6 [01000"0"00101011110010010011110110]

44AF24F6 [01000"1"00101011110010010011110110]

#2:

After Manual calibration (Register 6[27-bit]=1), toggle Register 6[22-bit]

C0AF24F6 ["1"1000"0"00101011110010010011110110]

C4AF24F6 ["1"1000"1"00101011110010010011110110]

#3:

After StartUp calibration (Register 6[27-bit]=0), toggle Register 8[7-bit]

20001808 ["0"100000000000000001"1"00000001000]

20001008 ["0"100000000000000001"0"00000001000]

Only in case of #2, LVDS clock output frequency was changed from 211.29MHz to 216.7MHz, but it was not the target setting of 207.36MHz.

Are there any other advices?

Thank you.

Best Regards,

Koshi Ninomiya

Hi Koshi-san,

I assume, DAC34H84EVM may have some default setting to program the device. Are the EVM able to program CDCE62005 with default value?

If it shows PLL lock at their default setting, then I think could help to tweak it for new frequency. Otherwise, we are not sure the device is operating properly or not.

Regards,

Ajeet Pal

Hi Ajeet-san,

When the customer reviewed the frequency settings, they noticed that the frequency settings were incorrect. The output clock frequency and VCO frequency were twice as high as expected. Because the VCO frequency was out of specification, the PLL did not lock, and the output clock was accidentally close to the desired frequency, so it seems that the customer had misidentified it.

Thank you for your support.

Best Regards,

Koshi Ninomiya