Part Number: LMK04828

Hello Guys,

Good day.

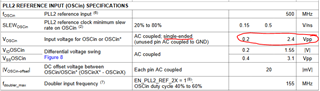

According to our customer single-ended AC coupled inputs in the LMK04828 evaluation module (SNAU145B-May 2013 - Revised march 2018) uses the negative input for OSCin_N and CLKin_N instead of the positive leg _P. Is the "inverted" input connection necessary or using the _P inputs for these single-ended signals also acceptable?

Also, just like to confirm if the OSCin inputs in AC coupled single ended config can be driven by a 3.3V signal?

Thanks and regards,

Art