Hi Team,

Do we have an information about the continuous output current, IOH and IOL?

Thank you in advance.

-Mark

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

Do we have an information about the continuous output current, IOH and IOL?

Thank you in advance.

-Mark

Hello Mark,

IOH = (VOH-VDDO/2) / 50

IOL = (VOL-VDDO/2) / 50.

For example, for a VDDO of 3.3 V:

IOH min = (2.64 - (3.3/2))/50 = 19.8 mA

IOL max = (0.66 - (3.3/2))/50 = -19.8 mA

Regards,

Kia Rahbar

Hi Kia, seeking for further support.

could you please also provide crosstalk information between the 2 inputs. We plan on feeding differential clock on one input and another Single Ended clock on the Single Ended input. If both clocks are running, we would like to know the impact on crosstalk.

Thank you.

Hi Mark,

we don't have that data available. We can do a measurement after the holidays.

What are the input frequencies?

regards,

Julian

Hi Julian,

The input frequency will be from 19MHz to 80Mhz

Our standard application will use 40MHz

Hello Mark,

If a clock is fed into both the LVCMOS input and the differential clock input, the effect of crosstalk will be minimal.

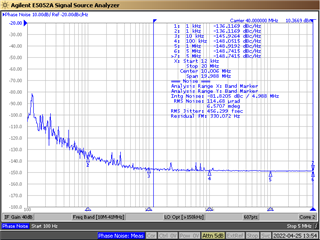

When only a differential clock is fed into the CLK input pins, the output clocks phase noise will be as follows.

Only CLK input fed a clock:

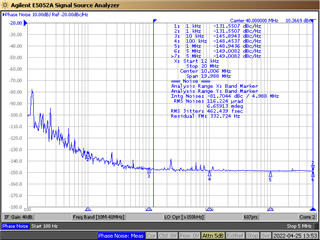

When both the LVMCOS input and CLK input are fed clocks, the output clocks phase noise will be as follows.

Both CLK input and LVCMOS input are fed a clock:

As you can see, the phase noise performance is quite similar in both cases and the rms jitter only increases by about 5 fs.

Also please note these measurements were taken with noisy clock inputs from a signal generator. The use of a better performing input will result in a better performing output.

Regards,

Kia Rahbar