Other Parts Discussed in Thread: LMK04832, CLOCKDESIGNTOOL

Hi,

I'm trying to implement the clocking requirement in TICS Pro software.

So as per the user guide those pins which I'm using I have to select power Down.

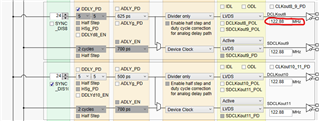

When I'm trying to set clkout_8,clkout_9,clkout_10 and clkout_11 with clock 125Mhz,but its considering default value 122.8Mhz.May I know why is not setting to 125Mhz.Anything other parameter has to be enabled?

Regards,

Nireeksha