Hello there

First of all, the purpose of this design is to using the GPS PPS to regulate the PLL of LMK05028 such that the output frequency is free from the temperature change.

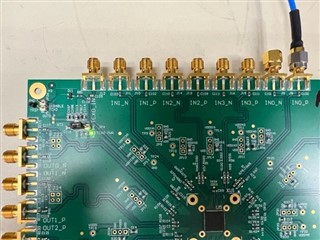

I didn't design the board, so I will do my best to describe it:

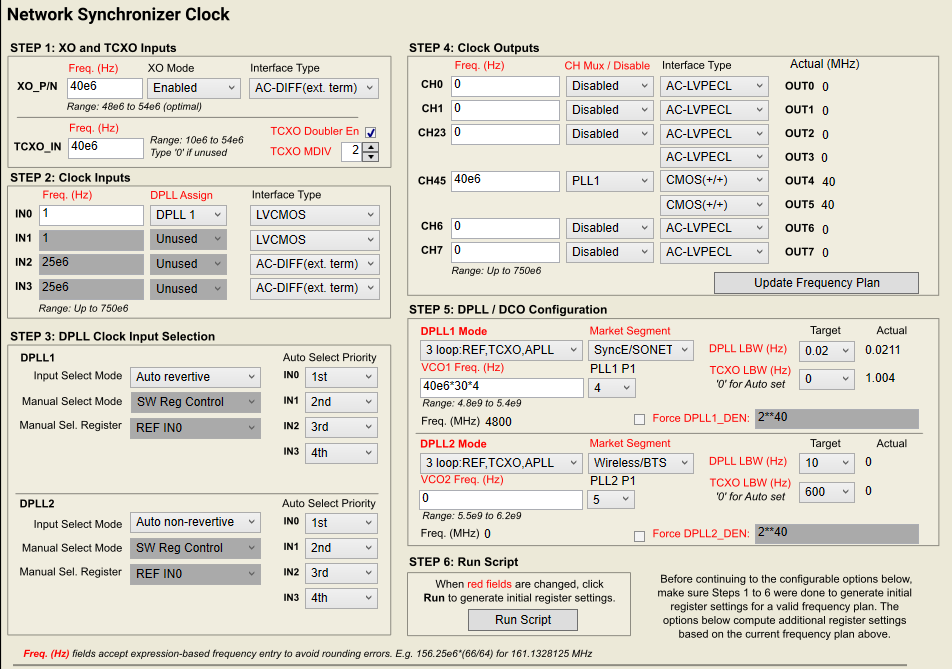

The XO and TCXO is connected to the same 40 MHz clock source;

The GPS PPS is connected to IN0 and then DPLL1

The output is located to CH4 and CH5, and required output frequency is 40 MHz too.

Not sure about the ZMD, maybe not necessary.

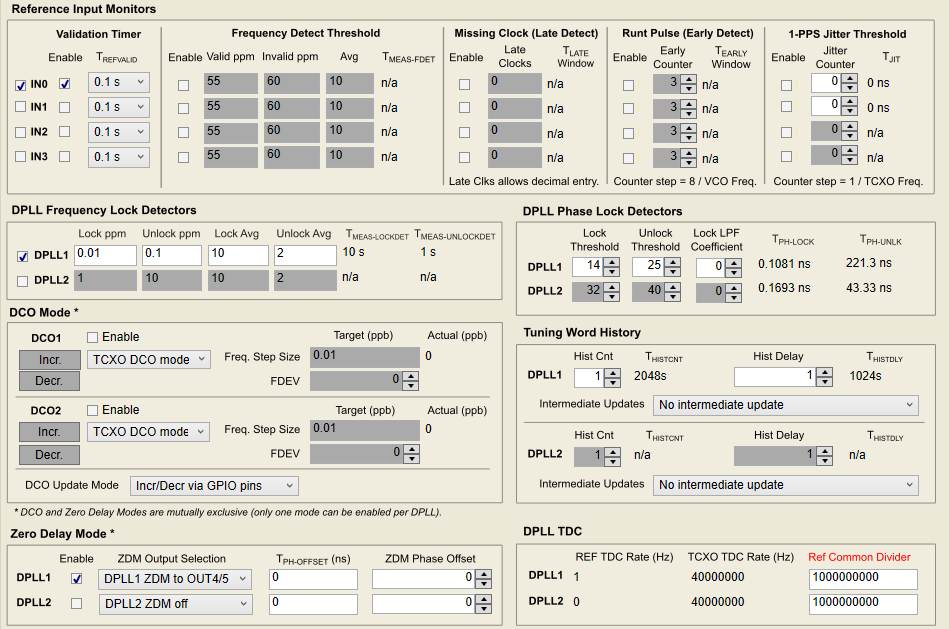

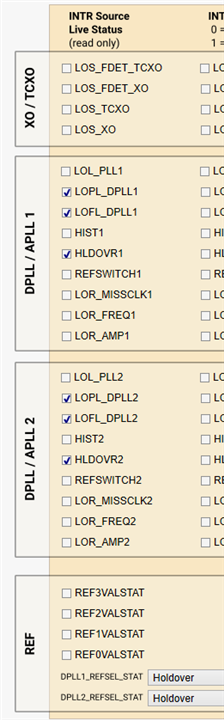

Anyway, after writing all registers using TICS PRO, the status report LOPL_DPLL1,LOFL_DPLL1 and HLDOVR1, so it lost the frequency and phase, and in the holdover mode.

After some modification, not sure what, but HLDOVR1 is gone somehow, but the LOPL_DPLL1,LOFL_DPLL1 are still there.

So what is the right way to configure LMK05028 to be regulated by the GPS PPS?

Is there something related to the duty cycle of PPS signal?

Thanks