Part Number: LMK05318B

Other Parts Discussed in Thread: LMK5B33216

Hello Expert,

Our customer is considering to design this part.

So there are some questions as below.

I want to get your feedback about each items.

1. If there is EVM or Design file (Schematic, PCB) or Design guide, please let me know.

I couldn't find them.

2. Is it possible to set OUT0/1, OUT2/3 to OUT0, OUT1, OUT2, OUT3 with different frequency outputs? Or is it the same frequency output?

Is it possible to output with separate frequencies? Are they tied together?

When I check register and block diagram, it seems to tied OUT0/1, OUT2/3 together.

3. When using two products for 16port output, is output clock skew control possible?

They want to remove clock skew on output.

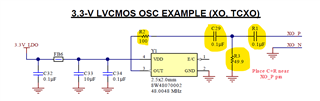

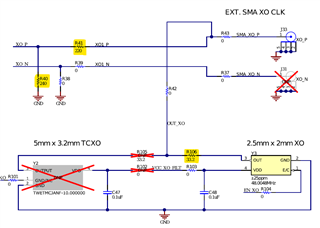

4. About Ref. Clock:

Can I use only either DPLL or APPL? or Should I use all of them?

They think that reference clock is burden.

When I check block diagram, I think that both reference clock input is needed.

5. What's minimum output frequency of AC-LVDS?

There is no commented on the data sheet.

Our customer need min. 100khz.

Best regards,

Michael