Other Parts Discussed in Thread: DAC3171, LMK01801

Hi Team!

My customer is interested in using DAC3171 to convert digitized ultrasound data to an analog output.

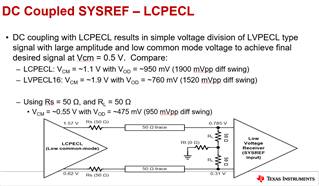

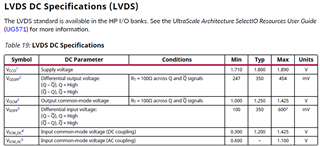

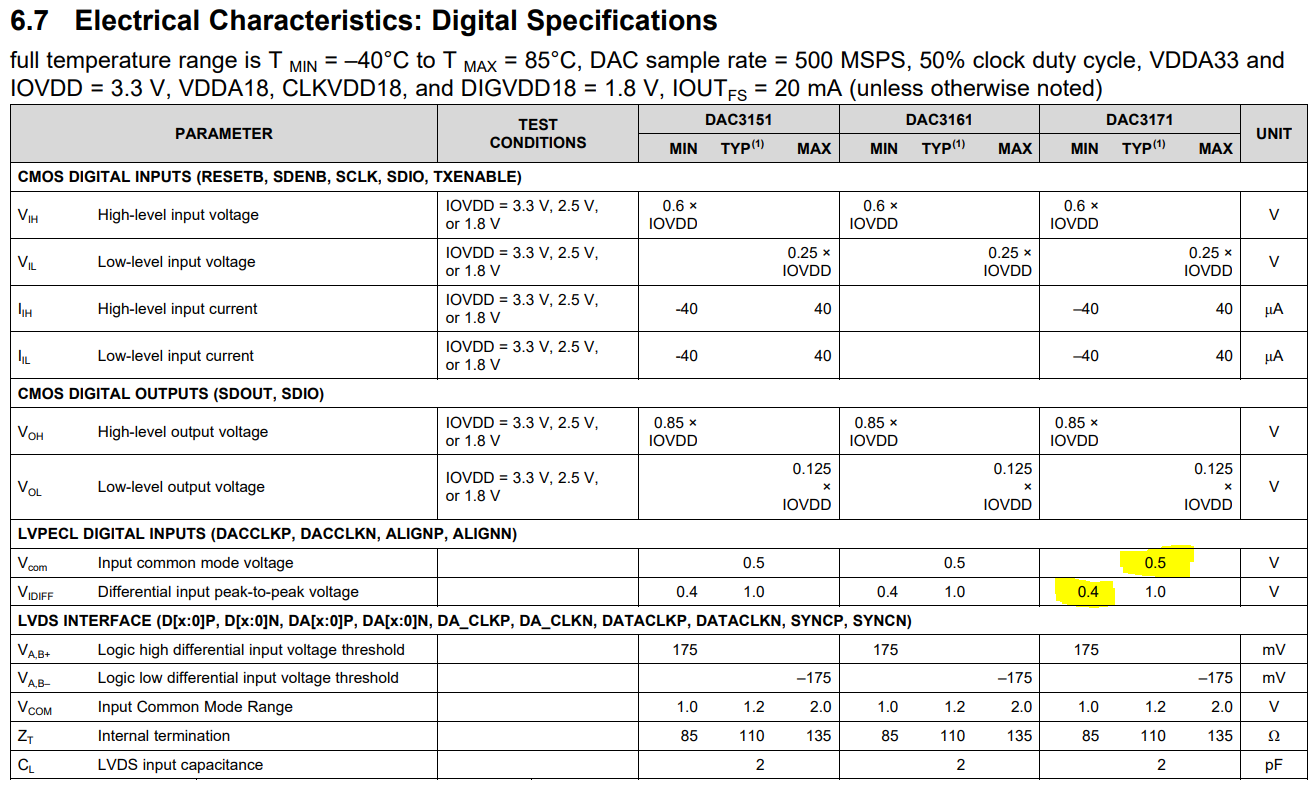

They want to use a 400MHz LVDS clock from FPGA to drive the DACCLK LVPECL pair of DAC. The LVDS driver side spec is shown in Fig 1. It looks the VODIFF is not bigger enough for LVPECL. Is there clock buffer IC can be used?

The clock need to provide:

The Vpp requirement for LVPECL clock input for the DAC3171 is a minimum of 400mVpp with the input common mode being 0.5V.

Fig1. FPGA

Fig2. DAC

Best regards

Shuai