My system based on LMK04616 generates 1000 MHz and 250 MHz clock output is HSDS.

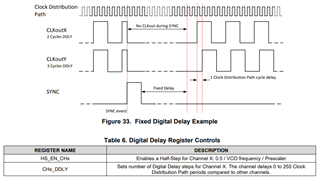

Clock distribution path is PLL2 VCO (= 6 GHz : 3) -> 2 GHz

WCLK = 1GHz (divided by 2)

CLK = 250 MHz (divided by 8)

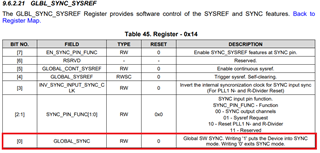

I am not able to issue 250ps digital steps while HS_EN_CH8_9 = '1'. Looks like Half-step is not enabled)

? Do we need to set others Register except 0x12B OUTCH89CNTL2