- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

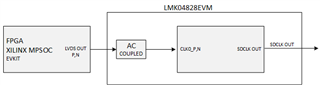

I configured it with evkit as shown in the picture below.

After setting pulse mode using clk0 port, SDclkout outputs undesirable signal in signal standby state.

If the LVDS signal of the FPGA EVKIT is separated, it is output stably to SDCLKOUT.

clk0 : bipolar mode

SDCLKOUT : LVDS OUT

Also, when continuous signal is applied, it operates normally.

Also, by changing CLK0 to MOS mode, it is normal when waiting for signals.

What will be the solution at this time?

Hello,

In order to use pulser mode, you would need to replace the AC coupling on the EVM input to a DC coupling.

Regards,

Julian

Hello,

Thank you for answer.

I am curious about the application of DC coupling.

For example, the wiring method of LVDS, CML, and LVPECL signals.

Regards,

Sungdae.

Hi,

For the DC coupled input at CLKin0, can provide the LVDS format input.

Thanks!

Regards,

Ajeet Pal