Other Parts Discussed in Thread: LMK03318, CDCE6214, LMK05318B

Hi team,

Sorry to bother you. But one of our customers needs your help with the configuration of the LMK05318BEVM. Requesting your kind guidance here.

I describe the problem as follows:

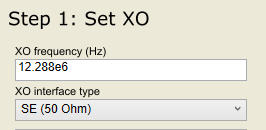

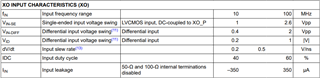

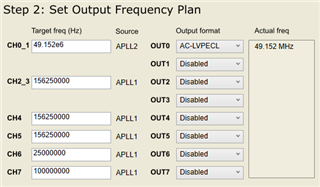

Use the EVM board for phase synchronization of the input clock and the output clock. Both the input and output clocks are LVCMOS levels, one input clock 12.288MHZ, one output clock 49.152MHZ.

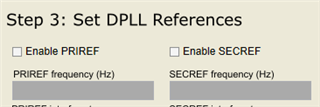

Requirements: When the input 12.288M clock phase changes, the output clock phase is also adjusted as soon as possible to align it with the input clock phase.

This customer asks if it needs any configuration other than the contents of the wizard? How is the content of advance configured? Do I need to select the ZDM feature? Could you help us provide a suitable configuration?

Best Regards,

Amy Luo